主题中讨论的其他器件: LMX2581、 LMK04828BEVM、 LMX2592、 LMX2582

大家好、Jim Seton、

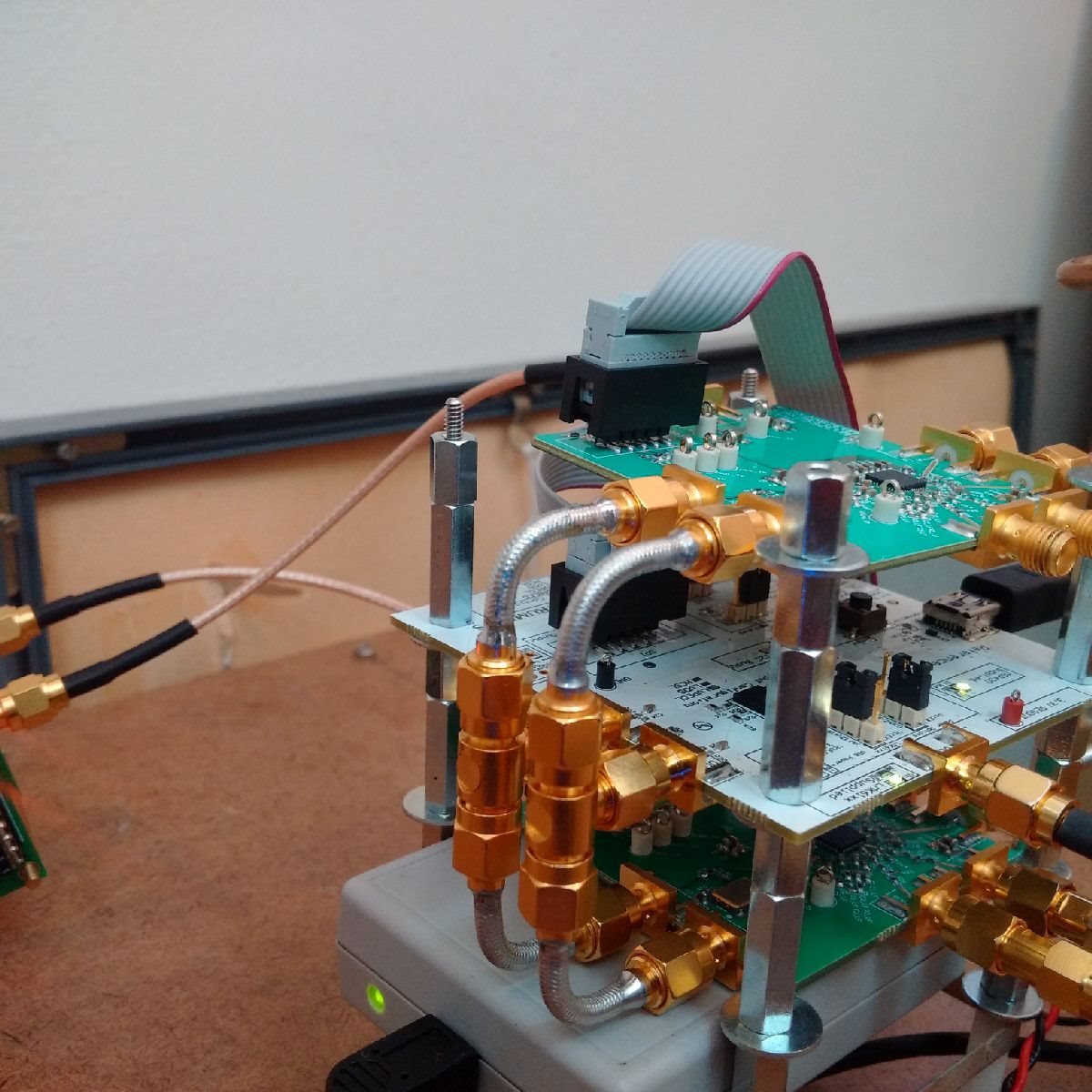

当我使用一个特定的 HSDCPRO .ini 文件时、我在使 DAC38RF82EVM 与 TSW14J56EVM 通信方面遇到了一些问题(没有闪烁的 LED、未成功传输外部模式文件):

DAC38RF8x_LMF_823 <=双路 DAC (12位分辨率)、实际值、4通道、2倍插值。

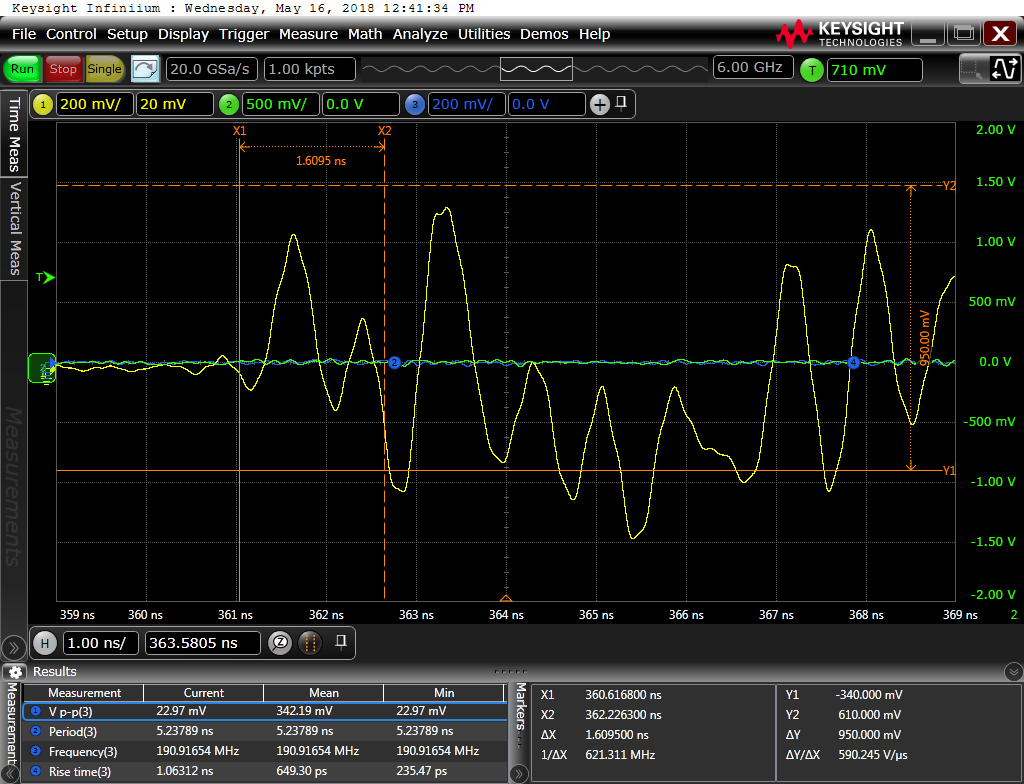

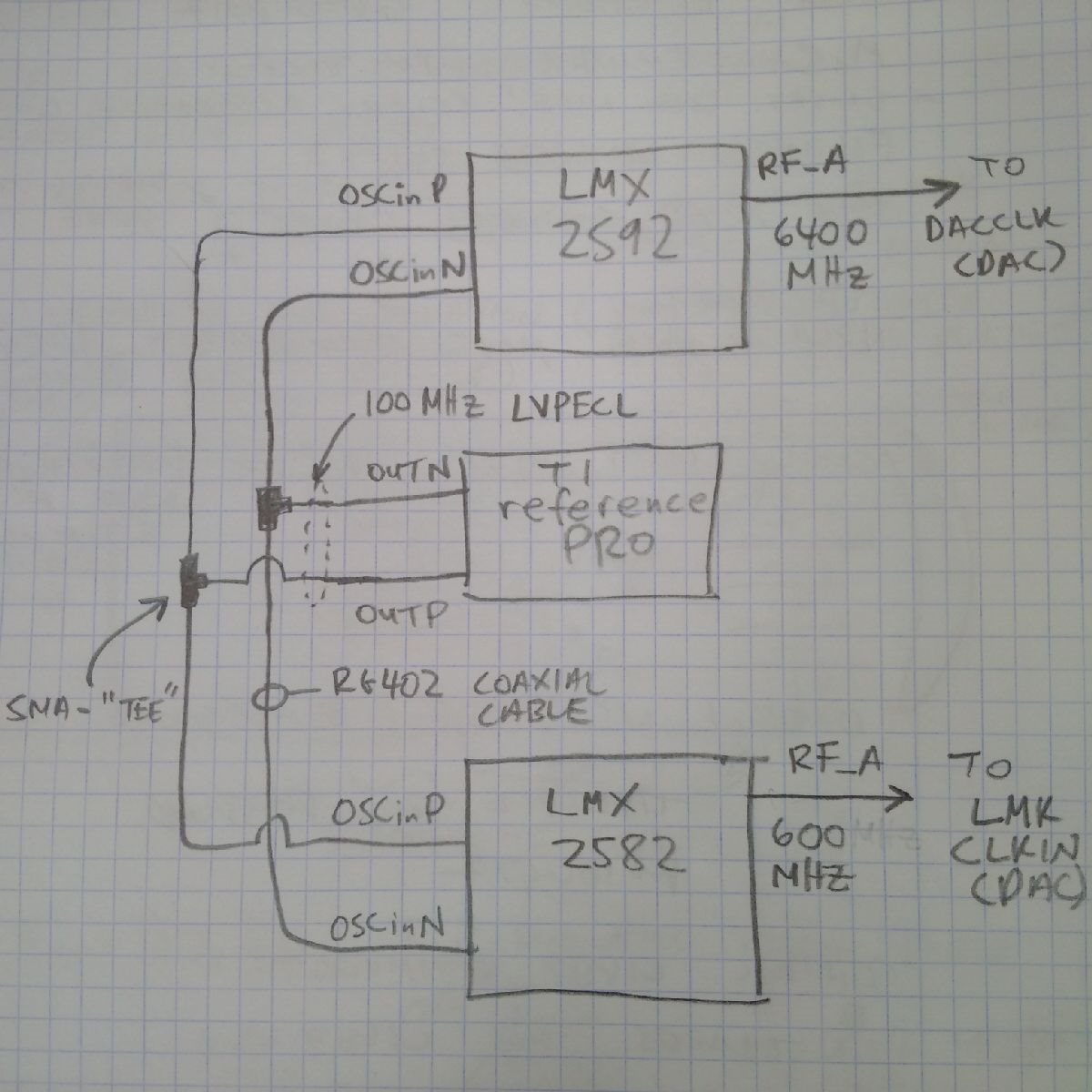

我使用的外部 DAC 时钟频率为6.4GHz (无杂散、~ 16dBm 音调、输入到 SMA" DACCLKP")。 使用完全相同的时钟设置,我*am*能够使用相关的 HSDCPRO .ini 文件:

DAC38RF8x_LMF_821 <=双路 DAC (14位分辨率)、实际值、4通道、4倍插值。

使用此.ini 文件、我可以与 TSW14J56通信(使 Tx CLK LED 闪烁、无存储器错误)、加载单音、加载外部模式文件、以及测量通道 A 和通道 B 端口(SMAS J6/IOUTA 和 J2/IOUTB_SE)上的预期射频输出。

是否知道为什么一个配置工作正常、另一个配置工作不好?

最后、我想使用以下设置运行 DAC:

DAC38RF8x_LMF_823 <=双路 DAC (12位分辨率)、实际值、4通道、1个插值。 3.2GHz 的直接外部时钟

但我需要一个射频合成器(我想是 LMX2581)、它将输出@ 3.2GHz 的纯净(无杂散)音调。

如果您能提供有关使用12位双路 DAC 配置的任何建议、我们将不胜感激。

非常感谢、

Steve Krupa

PS: 我正在运行 HDSCpro (v4.8)和 DAC38RF8x EVM GUI (v1.5)的最新 GUI 软件版本