Other Parts Discussed in Thread: ADS5444

你好

当我决定使用 Xilinx Spartan 6系列捕获转换器数据进行初始测试时、我想知道是否可以使用 SP6系列的 LVDS 时钟输出为转换器计时?

我搜索并发现了一些与此连接的可能性及其配置类型(终端电阻器等)相关的矛盾信息。

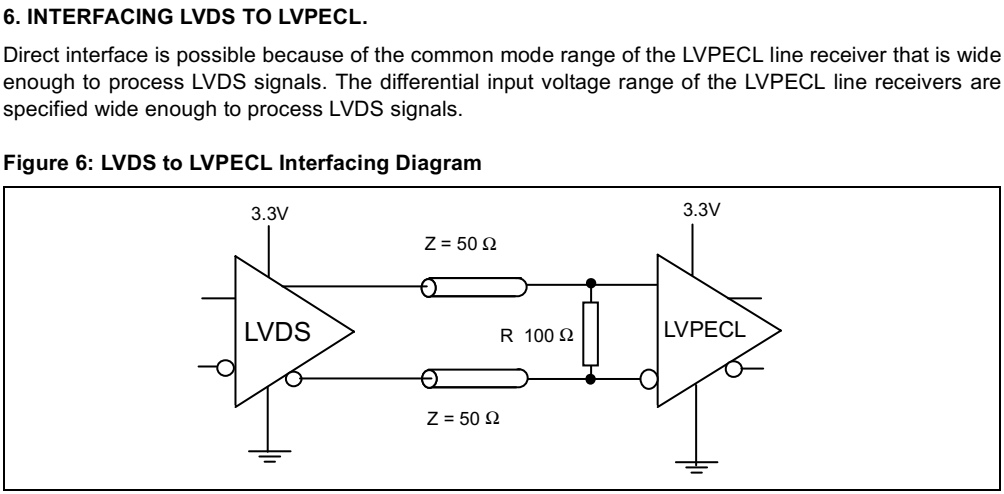

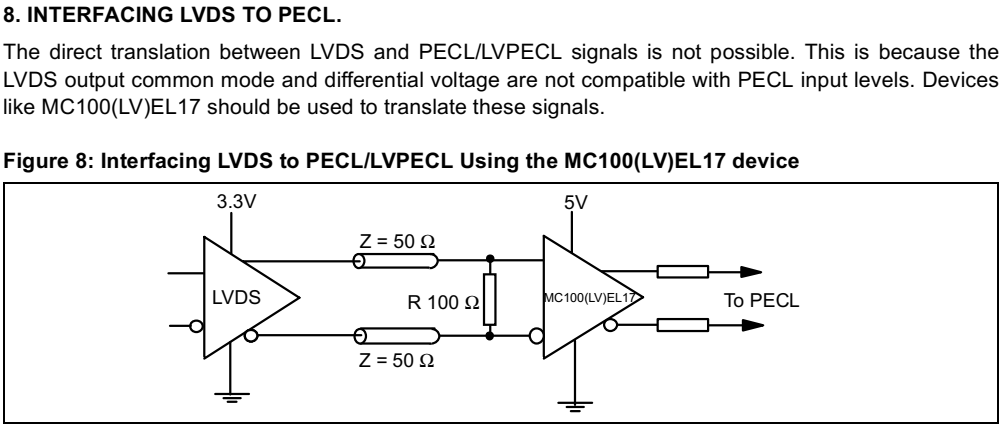

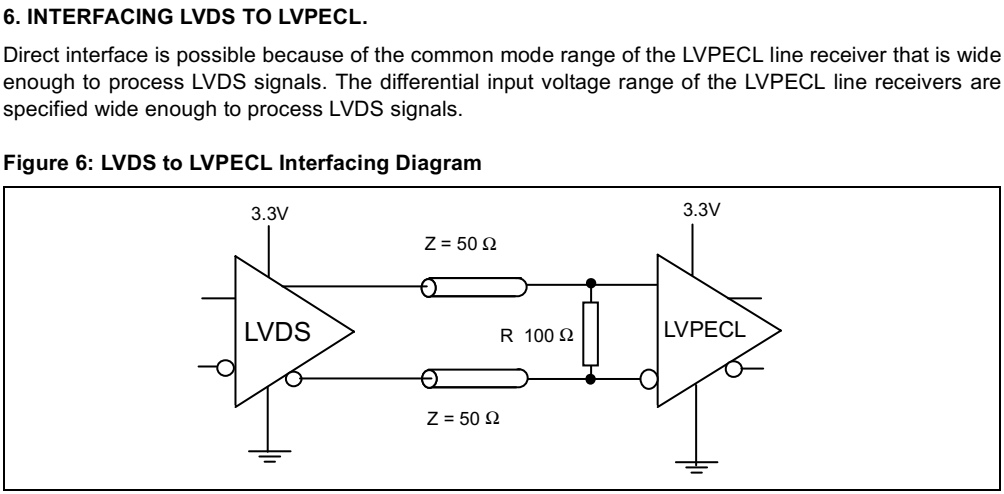

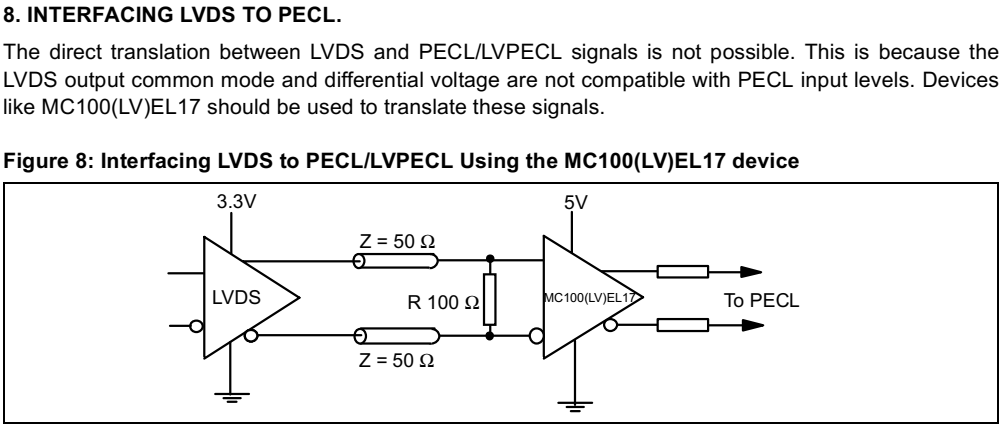

STMicroelectronics 的 AN1318标题为" LVDS 和高速差分逻辑系列之间的连接"、其中提到:

这些说法似乎是矛盾的。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADS5444

你好

当我决定使用 Xilinx Spartan 6系列捕获转换器数据进行初始测试时、我想知道是否可以使用 SP6系列的 LVDS 时钟输出为转换器计时?

我搜索并发现了一些与此连接的可能性及其配置类型(终端电阻器等)相关的矛盾信息。

STMicroelectronics 的 AN1318标题为" LVDS 和高速差分逻辑系列之间的连接"、其中提到:

这些说法似乎是矛盾的。

你(们)好

应该可以使用类似于6中所示的电路来使用 FPGA 的 LVDS 输出。 然后在 ADC 的每个 CLK 和/CLK 引脚的输入端直接添加一个100nF 串联电容器。 这些电容器确保时钟接收器的输入偏置为正确的输入共模。

请注意、由于 LVDS 信号的振幅仅约为0.7Vpp、ADC 性能将不是最佳(请参阅 ADS5444数据表的图24和25)。 FPGA 时钟源的抖动也可能大于理想值、这也会降低性能、尤其是在输入信号频率较高的情况下。

理想情况下、您应该在 ADC 时钟输入上使用振幅至少为1.5Vpp 的低抖动时钟源。 ADS5444数据表参考了以下有关计时的附加指南: http://www.ti.com/general/docs/lit/getliterature.tsp?baseLiteratureNumber=SLYT075

我希望这对您有所帮助。

此致、

Jim B