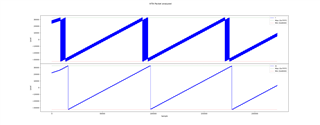

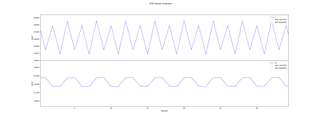

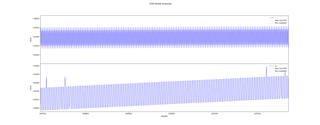

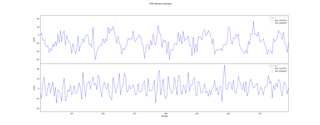

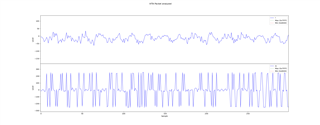

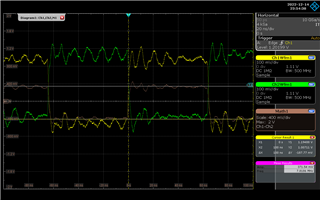

随机地、芯片将正确流式传输数据或将低字节的高位反转。 重置 JESD 会随机重新确定问题是否发生。 在不良运行时、高2位将随机反转。 我相信位5也会反转、但我不确定、因为本底噪声很难辨别。

其他意见:

- 该问题在 I 和 q 上单独发生

- 使用寄存器交换 LSB 和 MSB 使用的 JESD 通道会导致发送 LSB 的通道后面出现问题(问题出在数据而不是 JESD 通道)

- 启用快速 OVR 会导致最低字节始终为0 (预期)

- 非零的数字增益将影响直流偏移和本底噪声、但绝不会导致从反相位进入 MSB 的噪声(这意味着位翻转在数字增益之后发生)

- 将数字增益设置为0会导致所有数据为0 (这意味着位翻转在数字增益之前发生、与前一个点相矛盾)

- 在一次错误运行中、大约一半的样本是正常的、另一半的样本将受到此问题的影响

- 每次 JESD 复位时、这种情况发生的概率约为1/4

我们使用的是我们设计的板。 我们板的早期版本没有此问题、但我们在之前的版本中找不到此板之间的 ADC 状态有任何差异。