主题中讨论的其他器件: ADC14X250

您好!

我将使用 ADC14x250EVM 和 TSW14J56EVM 组合来捕获读取和捕获信号、如 SLAU625的图2所示。 我的项目的目标是通过光纤连接传输 ADC (SO+/-引脚)和 SYNCb 信号的输出。 我已经成功地通过光纤发送了串行输出信号、没有任何问题、但是我在使用 SYNCb 时遇到了很多问题。 因此、我对 SYNC 信号有一些问题:

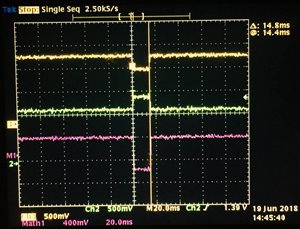

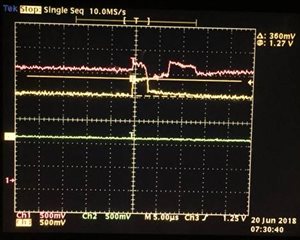

同步信号从接收侧发送、在本例中为 TSW14J56。 您能否解释同步信号工作方式的物理方面-我知道在连接时同步信号以大约14ms 宽度的脉冲进行断言和断言、如图1 (我连接探头并在 HSDC Pro 中按下捕捉按钮以获取同步信号)。 我希望这是从 TSW14J56板到 ADC 的通信、但是、当我断开连接时、我只能看到 FPGA 板发出大约3.5us 宽度的脉冲、如图2所示。

这意味着什么? 创建断言和取消断言的顺序是什么? 哪个芯片会产生置位和置位- ADC 是从 FPGA 接收3.5us 宽脉冲、然后断言 SYNC 信号、还是 FPGA 通过该脉冲断言信号、然后 ADC 在14ms 后断言?

图1. 原始同步信号

图2. SYNC 信号

ADC 配置 GUI 允许通过 SPI 控制同步。 如果我切换到控制 SPI 上的 SYNC 并在点击 HSDC 专业版中的"Capture"按钮后快速点击 ADC 配置中的"Deassert"按钮、我可以从 HSDC 专业版成功捕获信号。 但是、这并不实用。 我想知道是否可以使 HSDC 专业版中的捕获按钮自动取消 ADC 配置 GUI 中的同步? 换言之、当按下捕捉按钮但有一定的延迟时、连接这两个软件并使 SYNC 无效。 过去、TI 有人进行过此类集成吗?

感谢您的提前帮助。

Lizon