Other Parts Discussed in Thread: DAC8832, ADS127L11

主题中讨论的其他器件:ADS127L11、

您好!

我有一个使用 SAME70Q21 微控制 器的设计、其中 TI ADS127L11和 TI DAC8832连接到 SAME70主 SPI 外设的相同实例("SPI1")。 此 SAME70 SPI 外设允许多达4个不同的 SPI 从器件连接到4个芯片选择实例中的一个。 此外、SAME70 SPI 外设被设计成允许这些从器件具有不同的 SPI CLK 相位和极性行为(即 SPI 时钟处于低电平或高电平、数据在时钟的上升沿或下降沿随时钟输出)。 此配置被称为"可变芯片选择"模式。

这将我介绍总线上的两个 TI 器件。

ADS127L11 ADC 需要时钟保持低电平空闲、还需要数据改变 SCLK 上升沿的状态、并在 SCLK 下降沿读取数据。

DAC8832 DAC 没有明确指出 SPI 时钟应处于 IDE 高电平、但它确实显式说明主微控制器应具有 SCLK 下降沿的数据更改状态。 然后、DAC 将在 SCLK 的上升沿捕获数据。

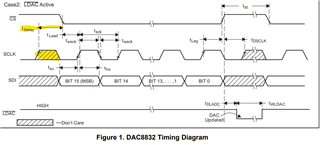

另请注意、DAC8832图1时序图似乎显示了空闲 SPI CLK 的无关状态。 下降之前的电压。 它还调用一个10ns 的"Tdelay"参数。 我是否正确地解释了这一点、即 DAC8832不关心 CLK 在 CS 下降之前处于什么状态、而只是在 CS 变为低电平之前它必须处于该状态至少10ns?

这会让我了解我使用逻辑分析仪观察到的情况。 我的 SAME70 micro 似乎正在正确处理多个从器件及其各自的 CLK 空闲状态。 主要问题是微控制器在开始 CS 置位和后续计时之前为该 CLK 空闲电平提供的时间量。

对于所有这些捕获、SPI 时钟配置为1MHz。 我只能在分析仪上以50MHz 的频率进行采样

下面是 ADWS127L11 ADC 的捕获:

我们可以看到、CLK 在该捕获开始时处于高怠速状态。 这是因为在 SAME70 SPI 外设上完成的最后一次访问是对 DAC8832的访问、DAC8832具有高电平有效的 CLK 配置。 在 SPI 访问结束后、SAME70会使 CLK 处于该特定从外设的空闲状态。 对于 DAC8832、CLK 保持高电平。 我们可以看到、一旦 SAME70开始与 SPI 总线交互、它会将 SPI CLK 延迟到该新的 SPI 从器件的空闲状态、而在 ADS127情况下、该状态为低电平。 这在 CS 变为低电平时有效发生。 然后、在图中、我们可以看到 ADS127LL 的适当 SPI 时钟数据关系、其中 ADC 更改 CLK 上升沿上数据线的状态、并将其锁存在下降沿。

我们看到 DAC8832的行为相同。 在此捕获中、与 ADS127LL 的交互恰好发生在其分析仪捕获之前的几毫秒、因此 CLK 处于低电平闲置状态。 然后、当 SAME70开始与 DAC8832交互时、它将 CLK 延迟到 DAC8832所需的 CLK 空闲状态为高电平、但它在 CS 变为低电平的几乎同时执行此操作。 但是、我们可以观察所需的时序和行为是否得到满足、数据线在下降时钟边沿发生变化、数据在上升时钟边沿被捕捉。

最后、当我在实际的硬件上运行时、这似乎可以同时使用两个从外设。 但是、我担心我可能会"刚好在边缘"计时、 如果这种计时完全在相应的芯片计时裕度内、我希望从 TI 获得反馈。

此外、虽然我可以调整 SAME70上的许多芯片选择和时钟延迟、但在可变芯片选择模式下、我无法在 尝试分析芯片选择之前明确指定时钟在空闲状态下的时长。

非常感谢您观看本演示。 请告诉我是否可以提供进一步的说明。