数据表在 第16页的加电复位一节中指出:"加电后、DAC8830引脚 VOUT 的输出为0V。"

在我们的硬件中、我们发现此语句并不总是正确的。 启动后、DAC8830 VDD 引脚具有5V 电压、基准电压达到5V、当我们开始与 DAC 通信时、我们可以预期通过 SPI 对 Vout 进行控制。 不过、在加电时和通信之前、有时 DAC 会在 Vout = 0V 时加电、而其他时候 DAC 会在 Vout = 5V 或2.5V 或3.4V 时加电。 我们在系统中使用其中的16个 DAC、每个 DAC 都有自己的稳定输出电压、当我们启动到这种"错误状态"时会达到该电压。 我已验证、除了上电时的单个上升沿外、我们的 SPI CLK 是安静的、请执行一个使 CLK 保持高电平的设计选择。 我假设这意味着在预期的通信开始之前、我不能将非零值加载到 DAC 中。

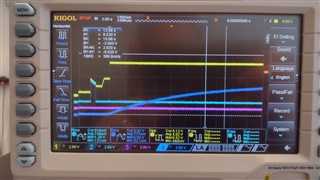

当 DAC 启动时 Vout = 0V 和 Vout 等于其他一些电压之间唯一的区别与我们的电压基准有关、该电压基准具有10秒的极慢时间常数。 当基准电压稳定为5V 并且我们重新启动系统时、每个 DAC 上的 Vout = 0V。 请注意、重新启动过程没有提供足够的时间来释放电压基准、因此当重新启动后 DAC 通电时、会出现5V 基准电压。 不过、如果该系统在经过长时间的等待30s 后首次开启、则 Vout 与 Vref 同步上升、直到 Vout 达到非零启动值。 Vref 需要10s 才能达到5V 电压的70%、因此在冷启动情况下、在上电序列期间不存在 Vref。

那么、我的问题是这个、POR 是如何实现的、 上电时 Vref 的缺失会以某种方式阻碍 POR 的功能吗? 或者、DAC 是否存在其他一些原因、可能以非零 Vout 启动?

感谢任何帮助。