您好!

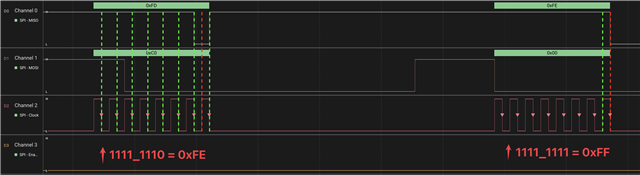

我遇到的问题与 此处 TI 论坛上所讨论的问题相同。 我使用的是运行 Arduino 引导加载程序的 Particle Xenon (nRF52840)。 运行代码以写入 CFR 并读回数据、切换通道、然后读出数据。 提到的问题是、正在读取的数据会向左移动1、例如、当我尝试使用 SPI 模式1 (下降沿)读取 CFR 时、我得到的响应为1111111_1101_111111H_1110 (0xFDFE)、 它实际上是 CFR 的左移默认值(0111_1110_1111111_1111 = 1111111_111111111_1110 >> 1)。 因此、我转而使用 SPI 模式0 (上升沿)读取 CFR、并回读默认值1111H_1110_111_1111。 然后、我使用数字信号分析器探测 SPI 线路:

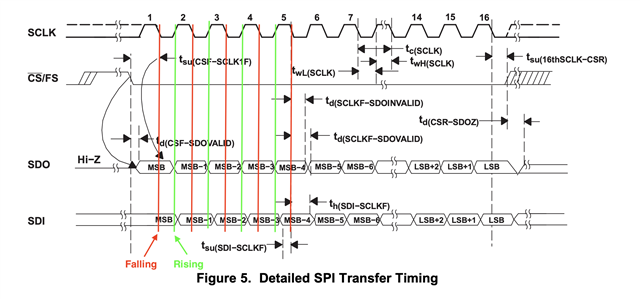

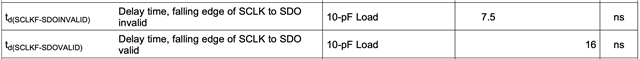

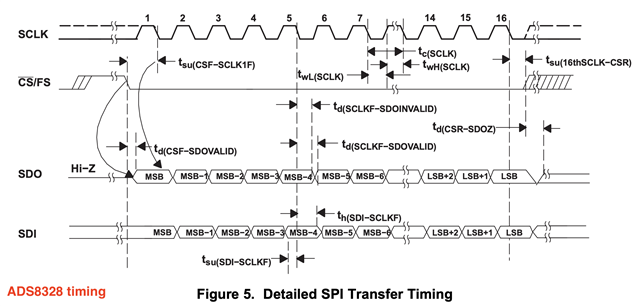

请注意、传输是通过将 CS 保持为低电平逐字节完成的。 我观察到的是、MISO (SDO)上的数据是在 时钟的下降沿输出(绿色虚线与红色虚线、显示了数据应该发生变化的地方)。 因此、如果我在上升沿(SPI 模式0)而不是下降沿(SPI 模式1)读取数据、该数据会正确读取为11111_111111H_1111。 现在这一切都是 有意义的,除了:

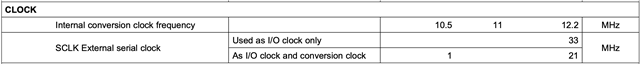

ADS8328数据通道声称该器件在上升沿推送数据、在下降沿读取(SPI 模式1):

2.如果我使用 SPI 模式0来写入 CFR 寄存器,这会失败,因为当我读回数据时,它会读回默认值。 如果我然后改为使用 SPI 模式1写入 CFR、但在 SPI 模式0下从 CFR 读回、则可以这样做、我读取正确的数据、例如、我发送1110_0110_1111_1101并读回1110_0110_1111_1101 (使用 SPI 模式1时、回读为1110_110_1111_1010、 因此向左移动1、并且违反了时序要求、因此有时数据可能会损坏)。

考虑到所有这一切、看起来器件会在下降沿推出数据、而在下降沿读取数据、这实际上并不是一个标准、因为我需要使用 SPI 模式1从 MCU 写入数据、 但使用 SPI 模式0读回数据。 我会这样做、但由于某种原因、当我尝试更改要从中进行数据采样的通道时、该设置不起作用。 如果我使用 SPI 模式1来选择通道并读回数据、则此操作有效、并且仅对一个通道进行采样(尽管我会丢失一位、因为数据已向左移动!)。 但是、如果我使用 SPI 模式1选择通道、然后使用 SPI 模式0读回数据、即使我在 CFR 手动切换中进行了设置、该模式也会继续交替使用该通道。

我很困惑为什么设备能正常工作、并想听到一些关于如何使用它的建议/指导。 如果有合适的替代芯片、我不介意更换它、尽管我需要2个通道、单基准、16位单端 ADC。