主题中讨论的其他器件:ADS1278

您好!

我使用两个 ADS1278、这两个都是 EVM-PDK 套件的一部分、但仅将 MMB0用于电源。 我已将其配置为 SPI 菊花链。 它们都配置为高分辨率模式和 TDM/固定输出。

我无法理解通过菊花链中的两个器件获得的数据。 我能够成功地从一个器件中读取8个通道。 现在、我将尝试从一个部分读取8个通道、从另一个部分读取4个通道。 我通过查看每个芯片的传入和传出信号、以确保情况正常、因为即使从 U2芯片也无法获得正常数据(使用数据表图81中的命名) 我假设其工作方式基本上相当于前8个通道值的时钟不采用菊花链形式。

我正在做的是:我已经将 CLK 减慢到512kHz、以查看高速连接是否存在问题、这似乎没有改善、但我在弄清楚这一点时、还是这样做了。 在进行测试时、我没有对 ADC 进行下电上电(或许我必须这么做?)。 启用中断

1.将 SYNC 引脚设置为高电平

2.启用512kHz 时钟

3.等待2^18/512kHz + 129/1kHz (0.641秒)。 我会尝试等到数据出现(数据表建议)而不直接读取 DRDY 引脚。 该时序如图84所示。 启动顺序。 此外、数据表2011年2月修订版的该图上方的句子中包含了"等待数据就绪后再生效 SYNC"的注释。

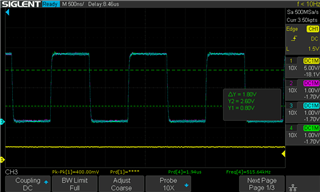

4.数据就绪(实际上只是如上所述的延迟)后、我将 SYNC 引脚置于低电平10us、然后再次变为高电平(在此期间 CLK 未停止)。

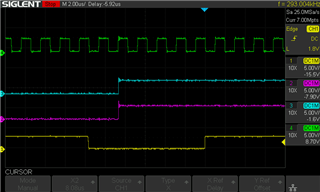

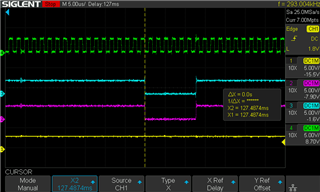

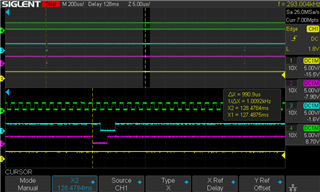

当我在示波器上观察时、我看到、在将 SYNC 置于低电平然后置于高电平后、两个芯片的 DRDY 引脚保持高电平约129个 Tdata 周期、如数据表所示。 然后、两个芯片的第一个 DRDY 低沿确实与预期的相同时钟下降沿对齐。 不过、两个芯片的下一个数据就绪脉冲未对齐。 我刚刚完成了此操作、一个芯片(根据数据表命名为 U2)的 DRDY 下降沿比 U1的 DRDY 下降沿晚了3个时钟。 当我让它运行时、DRDY 边沿不会保持同步并相互移动时间。

数据表中提示我需要检查仅来自 U1的 DRDY 引脚、但我想知道是否应该预计两个芯片的 DRDY 会保持同步。

我执行同步操作的方式可能有什么问题吗?