主题中讨论的其他器件: ADS8900B

大家好、

您能帮助我们解决客户的这个问题吗?

在数据表中、D_CKCS:SCLK 启动沿至(下一个)数据在 SDO 上有效。 起始边、前边或后边是什么? CPHA 和 CPOL 为0。

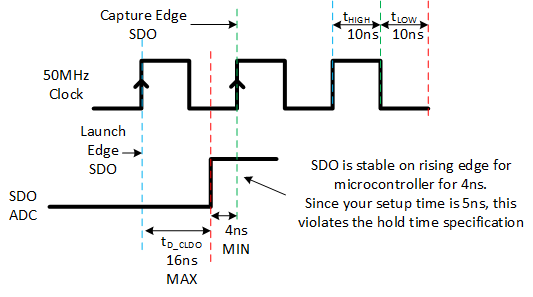

我们在50MHz 下运行 ADS7066 SPI 并希望了解 SDO 时序、以确认它已由 SCLK 后沿"随时钟移出"。

TD_CKDO 最大值= 16ns 会在我们的设计中带来问题。

TD_CKDO 最小值是多少? 最大值超过了半个 SCLK 周期、因此它错过了下一个 SCLK 前沿。 SPI 主器件的主器件的输入设置最小为5ns

尊重,

Danilo.