请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS8864 您好!

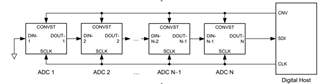

我们使用4件 菊花链连接中无繁忙指示器的 ADS8864的说明、如数据表中所述:

数据表中规定了:

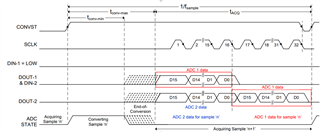

需要总共16 x N 个 SCLK 下降沿来捕获链中所有 N 个器件的输出。 可以在 SCLK 下降沿或上升沿读取数据。

然而、当使用15MHz SPI 时钟时、似乎需要(16 x N)+ 1个 SCLK 下降沿。 第一个下降沿似乎不会移出测量数据、但第二个下降沿会移出测量数据。 不使用占线指示器。 由于更好的稳定性、读取在 SCLK 的上升沿进行。

使用额外的字节读取和左移读取数据可实现额外的时钟周期。 但当我将 SPI 时钟频率更改为30MHz (如下所示的屏幕截图)时、1个额外的 SCLK 下降沿似乎是不够的。 现在、只有在使用该(16 x N)+ 2个 SCLK 下降沿时、数据才是稳定的。

我无法理解该行为。 我试图延长 CONVST 信号的上升沿与 SCLK 启动之间的延迟(从1.5us 到3.1us)、但行为没有差异。 您能否解释一下出现这种行为的原因? 我能够获得稳定的数据、但我想了解 IC 的行为、以防止特性中出现意外输出。

谢谢