您好、TI 专家、

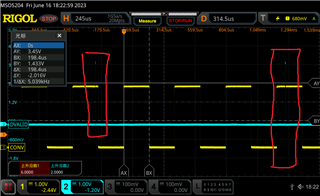

我发现 DAVLID 变为高电平有效而不是低电平、并且在始终切换 CONV 后不会变为有效。

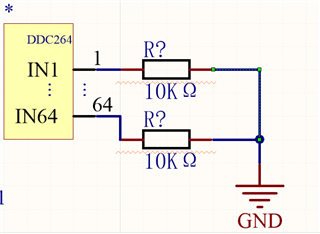

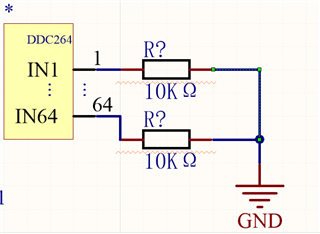

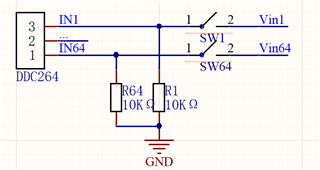

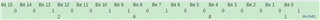

我 已经将模拟输入引脚与10kΩ Ω 电阻器和 GND 串联、如下:

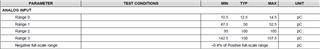

但我在"测试 模式关闭"的情况下接收随机数据。

在"测试模式打开"中全部为零。

当我的客户发送命令以获取数据时、我只是在 DAVLID 移动后执行 DCLK 操作。

问题出在哪呢?

否则、什么会使 DAVLID 输出异常?

感谢您的答复。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 专家、

我发现 DAVLID 变为高电平有效而不是低电平、并且在始终切换 CONV 后不会变为有效。

我 已经将模拟输入引脚与10kΩ Ω 电阻器和 GND 串联、如下:

但我在"测试 模式关闭"的情况下接收随机数据。

在"测试模式打开"中全部为零。

当我的客户发送命令以获取数据时、我只是在 DAVLID 移动后执行 DCLK 操作。

问题出在哪呢?

否则、什么会使 DAVLID 输出异常?

感谢您的答复。

您好!

我会让简先生深入了解更多细节、但只需几 件事:

希望其中一些内容可以帮助您找到问题、

教育

大家好、TI 专家 Eduardo Bartolome。

谢谢您的建议、让我更清楚地描述我的问题并添加一些详细信息。

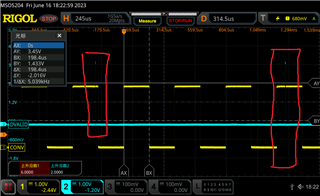

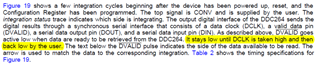

1.起初我以为 DVALID 会正常工作、不管 DCLK 的状态如何、所以当我想把数据发送到 PC 软件时、我才刚移动 DCLK、直到我看到8.1概览。然后我开始在 DVALID 每次低电平后移动 DCLK、它使 DVALID 正确。

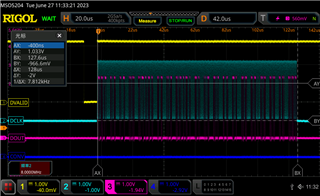

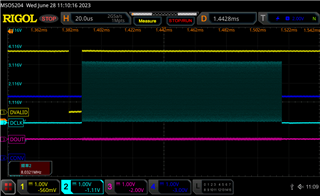

2.是的,它是 DCLK 作为标签显示在第二个帖子,第二张图片。

您是说 DVALID 应该在 DOUT 开始输出之前不断下降和上升吗? DOUT 操作应持续1024*(1/8MHz)= 120us?

我需要把它读出来。

10kΩ 我的模拟输入设计器件如下所示。当样品送达时、SW1至 SW64将闭合。连接了与0 Ω 电阻器和 GND 串联的模拟输入引脚。

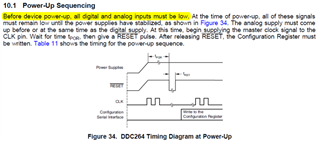

因为10.1上电时序要求显示"在器件上电之前、所有数字和模拟输入都必须为低电平"。

根据您的建议"输入端的10KOhm 接地有一定的风险"、我应该在电源稳定后将其移除或断开它吗?

5.代码4095?抱歉,我没有代码4095的相关信息。

感谢您的答复。

尊敬的 Jeyin:

第一个问题肯定是这样的。

在#2上,我的问题是,如果 DCLK=8MHz?

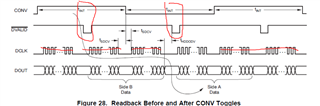

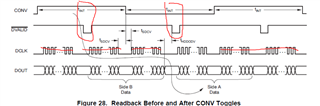

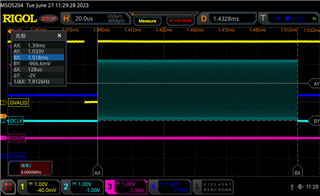

在#3上、是的、通常的步骤是 DVALID 下降、然后你发送 DCLK、DOUT 开始上升、DVALID 上升。 但在图中、DOUT 甚至在 DVALID 出现之前就开始出现了?

是的、在图片中、DOUT 的持续时间比另一张图片中的更长。 如果按照#3、你的 DCLK 为8MHz、那么是的、它应该为64x16/8MHz。

对于4号、我很抱歉误解。 是的、不需要将模拟输入连接到 GND、任何东西都不需要。 您只需连接探测器。 如果未连接模拟输入、在加电期间、没有问题。 实际上、输入端始终接近于 GND、因为它们已经具有内部二极管。 意思应该更像是、不要将它们连接到某个电压... (正常悬空)

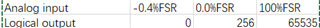

在#5上、它并不明显、但如果您检查 DS、在电气特性表中、它会显示"负满量程范围"为-0.4%。 这意味着逻辑输出零实际上是 FSR -0.4%的电流输入。 在代码中、即大约2^20 x 0.4%=~4095。 即、当输出是~4095代码(+/-偏移误差)时、输入的电流实际上为零。

请告诉我这是否合理... 希望它有所帮助!

教育

大家好!

<1> 是、DCLK = 8MHz。

<2> 当模拟输入悬空时、我收到零。

<3> 我已经检查了#3、这很 奇怪。

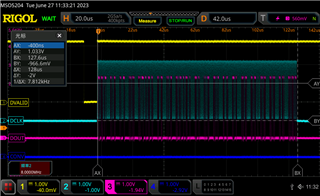

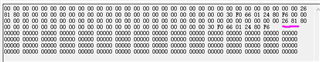

在某些情况下、DOUT 将在 DVALID 出现之前开始出现、如下所示:

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

第一部分 DDC264:

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

当模拟输入悬空时:

////////////////////////////////////////////////////////////////////////

当 连接与10kΩ Ω 电阻器和 GND 串联的模拟输入引脚时。除 IN20、21、23、24、25之外:

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

当连接至 sample 时。1:

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

当连接至 sample 时。2:

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

第二部分 DDC264:

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

当 悬空时:

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

当连接至 sample 时。1:

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

当连接至 sample 时。2:

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

您好!

实际上我认为现在一切都很好。 我很困惑、但我的同事指出、DDC264实际上会在降低 DVALID (请参阅图23)之前设置要传输的第一个 DOUT 位、并保持该状态、直到 DCLK 进入。 因此、如果第一个位为零、在第一个 DCLK 出现之前您不会在 DOUT 上看到任何转换... 但如果它为1、它将在 DVALID 之前切换并保持该状态、直到 DCLK 进入。 因此、您发送的所有数字似乎都正确。

DOUT 的长度看起来也很正确:16 x 64 / 8MHz = 128us。 最后一幅图显示了138us、所以有一个错误、但您的8MHz 可能不是正好是8MHz?

除此之外、我想您需要考虑数据传输方面的因素。

剩下的"唯一"事情是您的输出代码:

一些问题:

此致、

爱德华多

好日子,爱德华多

实际上我觉得现在一切都很好。 我很困惑、但我的同事指出、DDC264实际上会在降低 DVALID (请参阅图23)之前设置要传输的第一个 DOUT 位、并保持该状态、直到 DCLK 进入。 因此、如果第一个位为零、在第一个 DCLK 出现之前您不会在 DOUT 上看到任何转换... 但如果它为1、它将在 DVALID 之前切换并保持该状态、直到 DCLK 进入。 因此,您发送的所有数字似乎都正确。

感谢您的回复。我刚刚注意到图23。

DOUT 的长度也看起来很正确:16 x 64 / 8MHz = 128us。 最后一张图显示138us、所以有一点错误、但您的8MHz 可能不是正好是8MHz?

<1>蓝色是 DCLK,它的频率数据在图的左下角。光标是 DOUT,它在 DVALID 前面切换,一直保持到 DCLK 进入,所以显示138us。

在没有输入(#2)的情况下,它不应该是零,但应该是256 (20位中为4096,16b 模式中为256)。

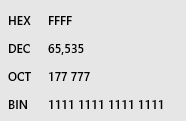

<2>我不明白你的意思。但16位是65535在 DEC ?

电阻器(如果有)应饱和至零,而不是全部饱和。

<3>我在数据表中没有看到它应该饱和到零或全饱和。但我在测试模式中得到了零。

这是您的电路板还是我们的 EVM?

<4>它不是 EVM。

您是否将其放在屏蔽盒内? 输入十分敏感、可以检测与其耦合的任何噪声。 不过, 我不认为这会显示为零。

<5>我不把它放在屏蔽盒内。有时我会得到大约 数百的数据输出。

您能用测试模式显示输出图吗?

<6>作为<3>

为什么要 为10k 案例附加4张图表? 它们是否都相同?

<7>它只是一种显示格式,看起来清晰整洁。

您在样片之间有什么变化? 我的意思是、样本零点似乎 卡住、但样本1看起来像是在切换(具有小输出代码)、而样本2看起来也在切换(但非常大)。 在没有任何连接到输入的情况下、您是如何实现如此大的变化的? 更奇怪的是、第2个器件的行为是相同的。 怎么回事? 两个设备是否独立?

<8>我的客户想要检查行为类似于电容器的样本的状态或质量。 我将其称为 C。因此、他们将为 C 充电一会儿、然后切换到 DDC264模拟输入、以查看可以向 C 充电的功率大小。样本1可能是糟糕的 C 或没有为足够的功率充电。

这两个器件是独立的。

此致、

jieyin。

<1>马上清除、哎呀!

<2>在没有输入(输入断开、悬空、零电流输入)的情况下、20位的输出代码约为4095 (我在上一篇文章中对此进行了说明)。 但您使用的是16b、我相信它更像代码256。

<3>它不特定于数据表。 基本而言、如果您在输入端和接地端之间放置一个电阻器、则由于输入端将具有相对于接地的一些残余正电压、因此将有电流从引脚流出、这基本上是负方向的。 因此、它将饱和至所有零。

测试模式不应全为零。 它应接近代码256。 我们可能应该把重点放在这一点上、因为这隔离了很多东西。 不过、我想不出你在做什么才会发生这种情况。 您能否共享原理图? 如果需要、您可以直接在我的电子邮件中执行此操作。 让我们进行 PM。 现在要去,但明天会回复其余的。

谢谢!

教育

您好!

基本上、如果我总结一下情况、根据<8>、我们不知道正常操作期间是否有任何错误(可能是对的)、但在测试模式下、会发现问题。 你同意吗? 这是您的担忧吗?

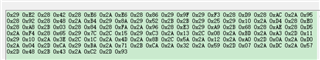

您将获得所有0、而不是接近256的值。 查看 CONFIG READ 数据、看起来您正在读取右侧配置(0x2681)、并且可以看到您确实正在对测试模式进行编程。 不知道如何获得这种效果。

但我们来检查器件是否在正常模式下正确转换。 您能否在一个输入端和一个直流电源之间连接一个1或10M Ω 的电阻器、并使用直流电源施加电压? 然后检查输出代码、看看它是否符合您的期望? 例如、施加0.1V 电压和1M Ω-->输入电流将为0.1uA。 如果使用1ms 的 CONV、输入电荷将为100pc、在16b 模式下应该会产生大约23k 的输出代码。 尝试直流源电压、以查看输出正是您所期望的...

最后一件事是、您能否确认 您的 CLK 是什么频率?

谢谢!

教育

Edu,你好。

很抱歉这么晚才回复。

<1>

在#5上、这并不明显、但如果您检查 DS、在电气特性表中、可以看到"负满标量程"为-0.4%。 这意味着逻辑输出零实际上是 FSR -0.4%的电流输入。 在代码中、即大约2^20 x 0.4%=~4095。 即、当输出是~4095代码(+/-偏移误差)时、输入实际为零电流。

我想我知道您的意思。您的意思是实际范围是-0.4%FSR ~ FSR (当-0.4%FSR、输出为零;0%FSR、输出2^16 * 0.4%= 261,100%FSR、输出65535时)。

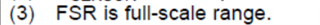

但 FSR 是满量程范围、

。

。

我的意思是、如果我选择 Range3、

,

,

FSR 为15pC (157.5-142.5)。

因此、实际范围为142.44~157.5pC

当不是电流输入时、它的0pC 比142.44pC 低、这使输出为零是合理的。我说的对吗?

让我认为、当测试模式为3.3伏时、

输出零。

输出零。

即使它有噪声、该噪声 看起来也太稳定、有意为之、以使输出保持为零。

<2>

但是我们来检查设备是否在正常模式下正常转换。 您能否在一个输入端和一个直流电源之间连接一个1或10M Ω 的电阻器、并使用直流电源施加电压? 然后检查输出代码、看看它是否符合您的期望? 例如、施加0.1V 电压和1M Ω-->输入电流将为0.1uA。 如果使用1ms 的 CONV、输入电荷将为100pc、在16b 模式下应该会产生大约23k 的输出代码。 尝试使用直流电源电压、以查看输出是您期望的结果...

这是个好主意,我会尝试它。

<3>

最后一件事,您能确认 CLK 的频率是多少吗?

CLK 为4MHz。

<4>

测试模式不能全为零。 它应接近代码256。 我们可能应该把重点放在这一点上、因为这隔离了很多东西。 不过、我想不出你在做什么才会发生这种情况。 您能否共享原理图? 如果需要、您可以直接在我的电子邮件中执行此操作。 让我们进行 PM。 现在要去,但明天会回复剩下的[/报价]我无权向您发送整个原理图、但我可以稍后将部分原理图发布在您的网站上。

<5>

顺便说一下、我的客户想要重新设计 DDC264板、能不能就布局和其他方面提供一些建议?

感谢您的答复。

此致、

洁殷

您好!

对于<1>、基本上是正确的: 实际范围为-0.4%FSR ~ FSR:

当-0.4%FSR 时、输出为零;

0%FSR、输出2^16 * 0.4%= 261

100%FSR、输出65535

不过、<1>的第二部分是不正确的。 该表中显示的所有内容是、当您选择范围3时、实际的 FSR (满量程)将在 142.44~157.5pC 范围内。 即、设置范围3时转换器饱和的电荷将处于该范围内。

在<3>上、这看起来太低了... 我相信您选择4分频时钟。 因此、转换器需要20MHz 时钟输入。 如果使用4MHz、则与 DS 中列出的正常时间相比、一切都要减慢5倍。 因此、ADC 转换需要更长的时间才能出现。 也很长时、积分时间可能没有问题。 请检查。

<4>不用担心。 如果您获得授权、请发送至我的电子邮件(我相信我已经在那里向您发送了一个附注)

<5> DS 有一些指导。 另一个来源是查看 EVM 布局。 我们没有任何其他文档、但如果需要、我们可以通过电话进行讨论。

此致、

教育

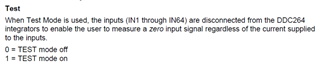

Edu,你好。

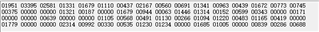

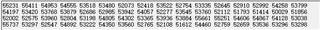

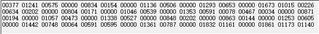

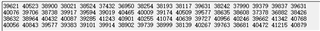

<1>我已尝试在一个输入和0.002V 直流源之间连接1.8KOhm。当 CLK = 10MHz 时、TIN = 40'000us DCLK = 16MHz、测试64次、得到这些数字。

它似乎不稳定。

<2>关于测试模式,我不知道。我想当设置测试模式时,输入会从 DDC264上断开,所以没有什么东西能影响 DDC264的"实数输入",对吗? 电源是否会影响"实际输入"?

尊敬的 Jeyin:

DC 实验太紧了... 我的意思是、理想情况下您不希望使用如此小的电压(2mV)、因为源可能不是很精确。 另一个问题是电阻器的另一侧连接到 DDC 的输入端、该端的电压也不恰好为零。 中的 DS 被称为直流偏置电压、对于低输入电流、该值通常为0.1mV (最坏情况下为1mV)、但可以随着电流的增大而增大(因为器件的输入阻抗不是零)、尽管我在这里并不认为这是一个问题。 不管怎样、为了消除所有这种不确定性并避免查看2阶效应、请尝试至少应用10个、如果不是100个 mV。

另一个问题是使用这样的小电阻器(1.8KOhms)。 我刚刚看到您使用40ms 的积分时间、不是吗? 这意味着您的最大电流只能为150pC/40ms=3.75nA。 使用1.8KOhms 时、您必须使用 UV 源。 我会说使用10MOhm。 这样、为了避免饱和、您的电压将小于37.5mV、比如30mV。 另一种方法是缩短积分时间、但我想这是您的运行点、您需要检查什么、所以将其保留在此处、然后尝试使用更大的电阻器。

第二个问题,你是对的。 测试模式应完全断开输入。 可能仍有一些泄漏、但应得到非零值的值。 即、150pC/40ms 的0.4%= 15pA、大于输入泄漏电流。

我建议、如果您进行<1>并且仍然卡住、我们会跳到一个呼叫中。 如果您认为这是一个好步骤、请随时向我发送电子邮件。

此致、

教育