Other Parts Discussed in Thread: DAC7563T

大家好!

我将使用外部基准和异步更新。

我的设置 如下:

Vout A -示波器

Vout B -示波器

3 -接地

4 - LDAC - FPGA 输出

5 - CLR -通过10k 连接到 GND

6 - SYNC - FPGA CS 输出

7 - SCLK - FPGA SCLK

8 - DIN - FPGA DOUT

9 - AVDD - 5.0V (带有适当的旁路电容器)

10 - Vrefin/Vrefout -连接到 AVDD

两个输出均从 AVDD/2 = 2.5V 开始

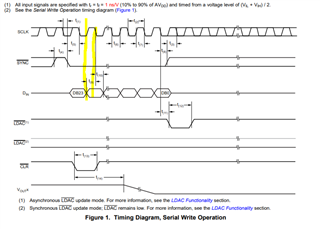

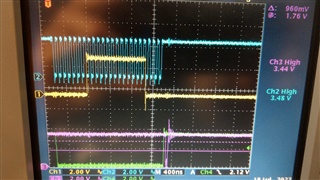

信号时序如下:

DAC 在每个命令集上都得到更新,似乎不存在任何计时问题。 如果我用0x00 0x00 0x00更新输出 A、它将变为0V 电平。 如果我随后发送0x00 0xFFF 0x00以更新输出 A、则只会进入~ Vref/2。 如果我发送0x01 0x00 0x00、输出 B 将不会改变(保持在 Vref/2)、但输出 A 同时达到最大5V 电平。

我在 DAC7563T 的两个采样中观察到此行为。 我根据表17尝试了其他命令位组合、并获得了相同的结果(或001没有更新)。 DAC 处于异步模式、并在 LDAC 变为低电平时更新、因此根据我的理解、我需要将命令位设置为000、并将 OUTA 和 OUTB 的地址设置为000和001。 我看到它更新正常、但输出错误的模拟电平、行为就像输出 B 成为输出 A 的基准一样。

内部基准是以某种方式启用的吗、或者我只是在两个采样上都有一个输出故障?