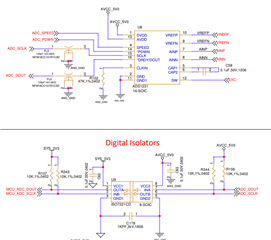

电路说明- MCU_ADC_DOUT、MCU_ADC_SCLK 连接到 MCU 端、ADC_DOUT、ADC_SCLK 连接到 ADS1231端。

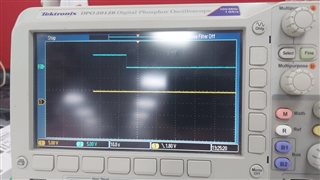

问题1 -我没有在 DOUT 引脚中获取数据值。 最初我已将 MCU_ADC_DOUT 引脚配置为 GPIO 引脚来读取数据。 当 MCU_ADC_DOUT 引脚变为低电平(数据就绪)时、我将此引脚重新配置为 SPI MISO 引脚、以读取转换后的数据。 MCU_ADC_DOUT 引脚没有变为低电平。 我已将一个称重传感器连接到 ADS1231。

怀疑2 - MCU_ADC_SCLK 引脚在最初是否有必要为低电平、以便 MCU_ADC_DOUT 变为低电平。

问题3 -请检查并验证原理图。

谢谢你。

此致、

内尔·马达夫