你好

我正在启动一个解调器、该解调器需要使用 ADC 将数据转换到 FPGA 进行信号处理。 我要将 ADC 配置为输出测试图形。 但 ADC 无法与 FPGA 链接、是否可以仅使用 Sysref 信号来链接 JESD?

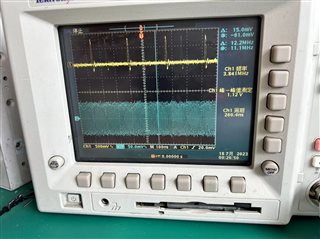

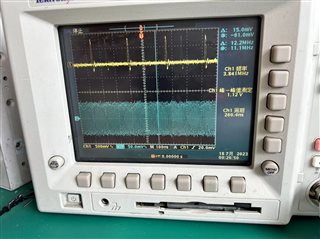

我已经上传了 sysref 和 clk 的波形、请帮我检查时序是否正确、黄色曲线是 sysref、蓝色曲线是 clk、clk 是122MHz

提前感谢。

祝你一切顺利

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好

我正在启动一个解调器、该解调器需要使用 ADC 将数据转换到 FPGA 进行信号处理。 我要将 ADC 配置为输出测试图形。 但 ADC 无法与 FPGA 链接、是否可以仅使用 Sysref 信号来链接 JESD?

我已经上传了 sysref 和 clk 的波形、请帮我检查时序是否正确、黄色曲线是 sysref、蓝色曲线是 clk、clk 是122MHz

提前感谢。

祝你一切顺利

尊敬的春松:

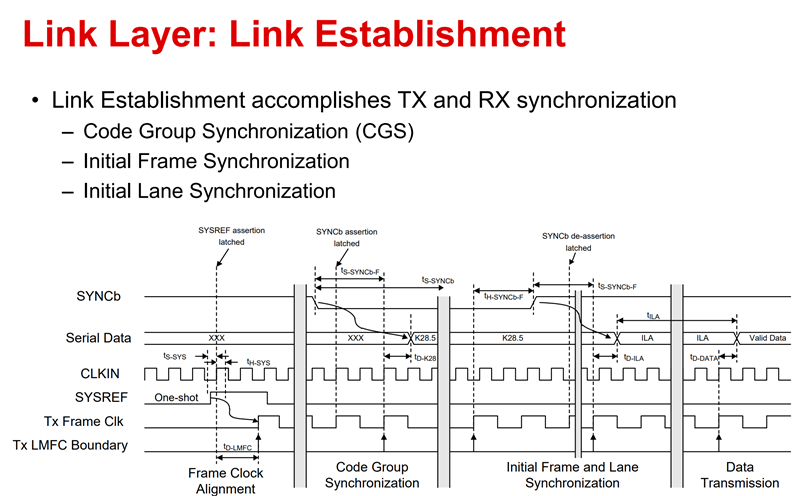

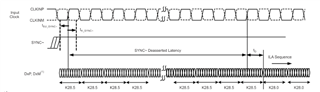

该器件需要符合 JESD204B 标准。 这意味着要开始启动到 FPGA 的链路、首先必须发出 CGS (代码组同步)请求。 这是通过将 SYNC 信号置为有效(低电平有效)来启动的。 CGS 阶段完成后、器件将进入启动过程的 ILAS (初始通道对齐序列)阶段、FPGA 将 在 ILAS 完成时取消对 SYNC 信号的置位、从而向 ADC 指示 FPGA 已准备好接收实际的采样数据、而不是 K28.5字符。

请参考此文档获取以下图片: https://www.ti.com/lit/ml/slap160/slap160.pdf

谢谢,Chase

你好,蔡斯

感谢 您的答复。

ADC32J25上没有 SYNCb 信号、这是否意味着 SYNCb 只是一个内部信号? 我只需要从 FPGA 传输参考频率信号。

从数据表中、我看到 SYNC 信号需要通过从低到高的转换来获得 k28.5代码输出。 这意味着我需要在 ADC 侧和 FPGA 侧同时连接 SYNC 和 SYSREF 吗? 目前、我只是连接 sysref 引脚。

祝你一切顺利

尊敬的春松:

对于这个器件、SYNCb 信号被称为 SYNCP~和 SYNCM~。 SYNCb 是一个低电平有效同步信号、与 JESD 器件配合使用以初始化链路。 如果没有此信号、则必须通过寄存器使用串行同步请求(这在设计期间不是推荐的方法、因为某些器件不支持串行同步请求)。 对于此器件、您可以使用寄存器0x3A 交换 SYNCb 脉冲。 这可以通过将 CREF 上的电压 同步请求 EN 设为1、然后切换 SYNC REQ 在 FPGA 开始 CGS 阶段后、该字段变为1并返回到0。 在本例中、只可以使用 SYSREF。

关于 SYSREF 频率、该值应为 SYSREF = FS /(N * K)。 在您的情况下、如果 FS = 122MSPS、K 是 JESD K 值(可在寄存器 CTRL K 和 每多帧帧帧帧数 )、N 可以是任意整数值、并且是灵活的。

谢谢,Chase

尊敬的春松:

如果您将 SYNC REQ EN 设置为1、这会将 ADC 置于串行同步模式、并忽略物理同步引脚的任何输入。 在 SYNC REQ 位被切换前不会发生任何操作。 请查找此资源有用: https://www.ti.com/video/series/jesd204b.html

如果将寄存器0x15中的 PDN PIN DISABLE 字段设置为1、则还必须将同一寄存器中的全局 PDN 字段设置为1才能关闭此器件。 PDN PIN DISABLE 字段只是告诉 ADC 忽略输入、而是使用寄存器设置进行断电。

谢谢,Chase

你好,蔡斯

我已经使用 SYNC~P/SYNC~M 替代 SYSREF 对电路板进行了一些返工、但仍然无法测量 数据输出布线上的任何波形。 我认为布线上应该有 K28.5波形。 ADC 是否可以在没有参考频率的情况下仅使用同步信号工作?

我发现数据表中的时序与 ppt 中的时序不同。 我已通过 FPGA 发送了一个从低到高同步的转换、如数据表中的图145所示。 但我没有在数据布线上看到 K28.5。 这意味着 SYNC 信号和 SYSREF 信号都应连接到 FPGA 吗?

FPGA 如何发送高/低转换? 在本例中、我是否可以在数据跟踪上看到 K28.5?

祝你一切顺利

尊敬的春松:

图145显示的是前一次 SYNC~转换到 CGS 阶段结束(也是 ILAS 阶段开始)之间的延迟。 确定性延迟需要 SYSREF、我们建议这样做(JESD204B 子类1)。 如果配置了器件、SYSREF 是有效频率、并且 FPGA 将 SYNC~信号从高电平切换到低电平、则器件应开始传输 K28.5符号。 这会将 FPGA ILA 显示为重复值0xBC。 您能否启用 SYSREF 并重试?

谢谢,Chase

你好,蔡斯

很抱歉延迟响应、我已改回使用 SYSREF。 但在配置之后、ADC 输出始终为高电平。

我的配置过程如下所示:

您能帮助检查我的测试设置是否有任何错误吗? 我是否需要将 SYNC REQ EN 设置为0?

祝你一切顺利

你好,蔡斯

很抱歉、我有另一个问题、它是否可以使用 SYNC 和 SYSREF 的单端连接? 由于 FPGA 缺少 GPIO 资源、我需要在下一次构建中节省一些引脚。

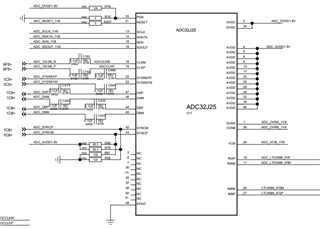

我已将我的 ADC 原理图放在这里、您能帮助评论一下吗? SyncP 和 SyncM 未连接到 FPGA、只需将电阻保留在外部。

我需要使用外部导线来连接它。 FPGA 输出似乎仍然有问题。 我必须使用手动同步。

祝你一切顺利

春松