您好!

我想对 SPI 接口的时序要求进行一些澄清。 数据表中讨论了 SDO (SPI 输出)所需的设置和保持时间。 它指的是什么? 我不认为输出通常会有设置和保持要求。

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我想对 SPI 接口的时序要求进行一些澄清。 数据表中讨论了 SDO (SPI 输出)所需的设置和保持时间。 它指的是什么? 我不认为输出通常会有设置和保持要求。

谢谢

大家好、Jason、

感谢您的发帖。

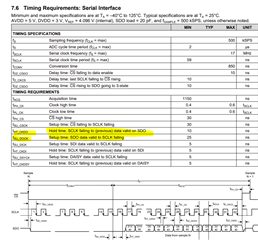

在这种情况下、设置时间(Tsu_dock)是控制器在 SCLK 上升沿之后必须等待的最短时间、然后才能在下降沿锁存数据。 换句话说、 25ns 是 SDO 引脚对于输出变化的稳定预期最长时间、以使其能够被读取。

保持时间(THT_CKDO)是在 SCLK 下降沿之后必须等待多长时间才能发出另一个上升沿、这会导致 SDO 更改为下一个位。 这可以确保 SDO 在捕获边沿之后保持稳定至少10ns 并且可以正确读取。

此致、

瑞安

大家好、Jason、

实际上、您是对的。 数据仅在 SCLK 下降沿启动。 捕获边沿在技术上取决于 控制器的计时能力、但我们建议在另一个边沿上进行捕获。

考虑到这一点、对规格的解释如下:

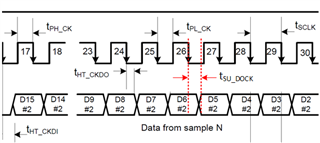

1. THT_CKDO:图1中已正确绘制。 为 上一个 在 SCLK 下降沿之后、数据位将在 SDO 上保持至少10ns。 只有当您尝试在用于转换下一个 SDO 位的相同边沿上捕获数据时、该规格才会变得重要。 如果您的系统无法可靠地将时序关闭保持在该规格范围内、则最好等到反向时钟沿读取数据。

2. tsu_dock:这仍然没有被适当地绘制。 建立时间应从时钟下降沿开始、并在数据转换稳定之前提前测量。 这会告知控制器在相反的时钟边沿读取新数据时(如上文所建议)等待多长时间。 我已将 Tsu_dock 重画如下:

此致、

瑞安