大家好、

我是一名来自华东地区的模拟 FAE、我在为 SUPCON 提供支持。

客户正在 测试 DAC8740H 以更换 AD5700、并符合一个问题。

测试背景:

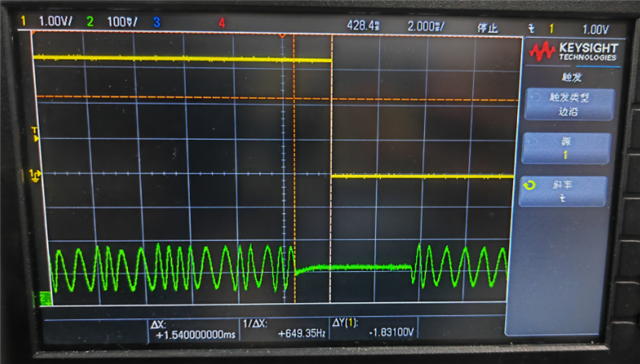

客户使用上部计算机通过 DAC8740H 调制发送 HART 信号、从而使用 MCU 读取 UART 结果。 它们的软件逻辑是、在捕捉 CD 引脚的上升沿时启用 UART、在捕捉 CD 引脚的下降沿时禁用 UART。

问题:

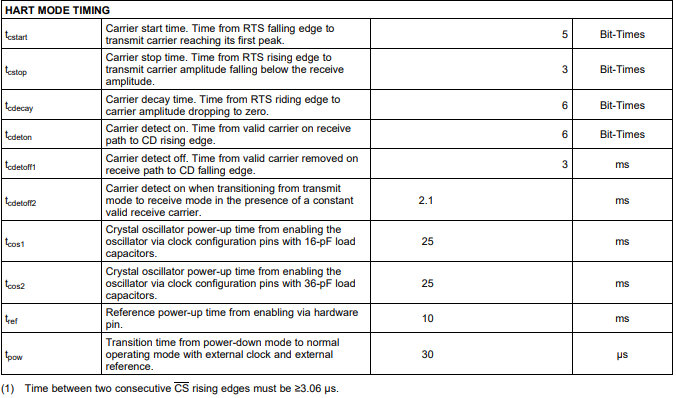

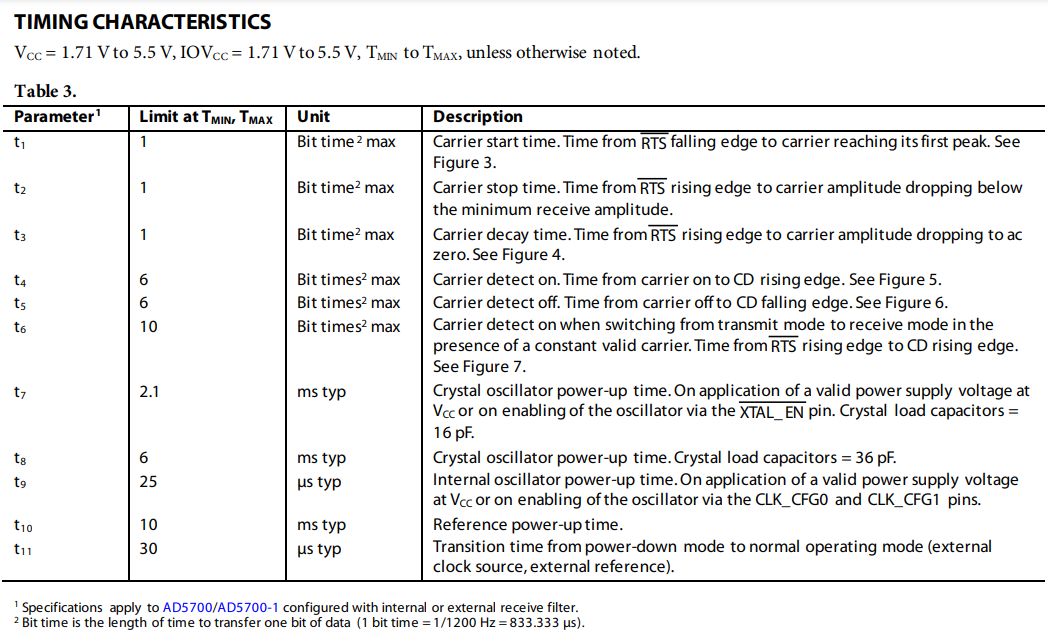

利用 DAC8740H、UART 信号很容易丢失最后一位。 调试后、根本原因是 CD 引脚被下拉太早、因此 UART 被禁用、上次数据传输未完成。 通过查看数据表、DAC8740H 具备3ms 载波检测关闭时间、而 AD5700具备5ms、我们能够延长 T cdetoff1? 或者是否有其他方法让 CD 稍后下拉?

DAC8740H 时序:

AD5700时序:

请帮我解决这个时间问题。 BTW、我还向 Joseph 发送了电子邮件、以便我们通过邮件传达更多详细信息。

谢谢。

周泽伟