请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC09QJ1300-Q1 大家好、

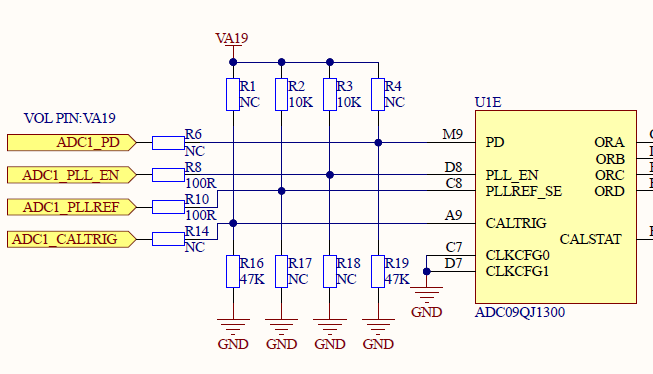

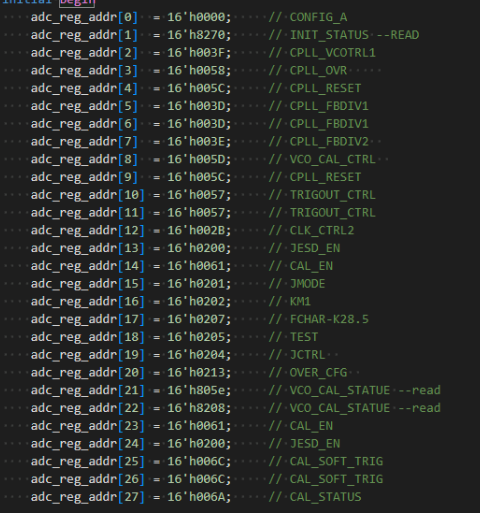

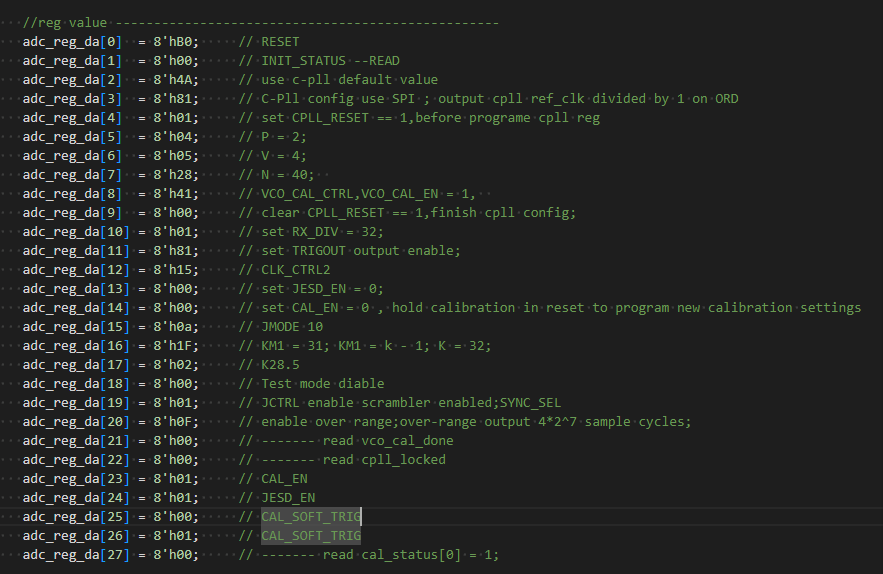

引脚配置:PD 配置为默认下拉电阻、PLL_EN、PLLREF_SE 默认被拉高、外部时钟被选为50M 信号输入。 寄存器配置地址和寄存器值按下图的顺序配置、实际上、ADC PLLREF_CLK 输出通常会输出50 MHz 信号、但 TRIGOUT±未设置。

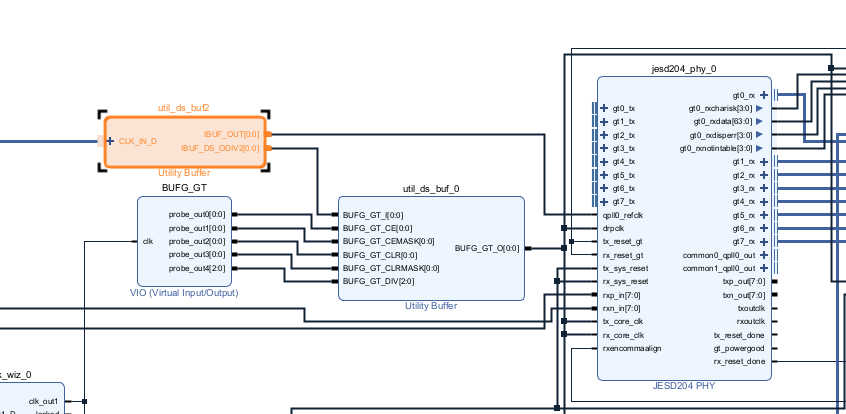

在原始设计中、设置被视为 FPGA GTH 恢复时钟、但现在显示没有输出。

当 TLR_OUT 进入 FPGA、然后进入 MREFCLK 时、MREFCLK 时钟频率始终不稳定。 FPGA 使用 ultersclae 架构 zukc060。

时钟连接如下:

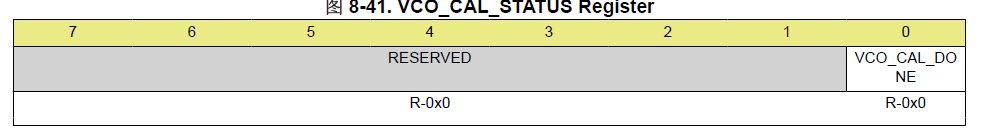

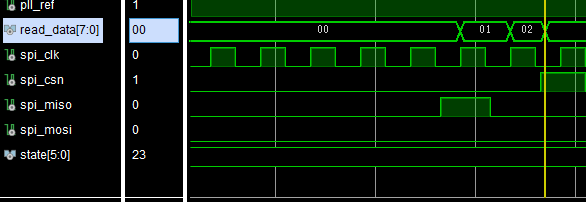

在配置过程中读取 VCO_CAL_STATUS、VCO_CAL_STATUS[7:1]是保留位、而0位是通过寄存器读取 VCO_CAL_DONE 状态位。

不过、在实际读取操作中、会在多次读取0x20之后读取0x30。 但采集触发时钟仍然不稳定。

您能帮助检查这个问题吗? 谢谢。

此致、

切里