主题中讨论的其他器件:LMK04828

在 ADC GUI 中、

在"EVM"选项卡上、我确实看到"FPGA 参考时钟"根据"#2b"中提供的输入具有20 (默认值)的分频因子。 外部 FS 选择"

例如:

#2b. 外部 FS 选择 = 4000

FPGA 参考时钟= 200

问题:是否可以在 ADC GUI 本身中将此除法因子修改为一个新的数字(Like16而不是20)?

最佳

贝朗

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在 ADC GUI 中、

在"EVM"选项卡上、我确实看到"FPGA 参考时钟"根据"#2b"中提供的输入具有20 (默认值)的分频因子。 外部 FS 选择"

例如:

#2b. 外部 FS 选择 = 4000

FPGA 参考时钟= 200

问题:是否可以在 ADC GUI 本身中将此除法因子修改为一个新的数字(Like16而不是20)?

最佳

贝朗

您好,Behrang,

FPGA 参考时钟不是外部 FS 的分频版本、而是 SERDES 速率的分频版本、这取决于 FS。 您可以使用以下公式计算 SERDES 速率和 FPGA 参考时钟。 FGPA 参考时钟分频器具体取决于您处于何种 JMODE、这是8b10b 或64b66b 模式。 如果它是8b10b、则分频器将为40、如果它是64b66b、则为66。

JMODE0、8b10b 模式

FS= 4000MHz

串行器/解串器速率= FS * r = 4000 * 4 = 16000 MHz

FPGA 参考时钟= SERDES 速率/ 40 = 400 MHz

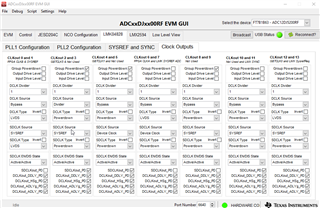

FPGA ref 时钟分频器默认设置为1、因此无论您在 SMA 输入 REF CLK 中提供的频率是多少、都将其分配到所有 LMK04828时钟输出、然后输出到 FPGA 中。 如果您要修改 EVM GUI 中的分频器、请转到 LMK04828选项卡、然后转到 Clock Outputs 选项卡、您应该会看到下面显示的屏幕。 然后、您可以将"DCLK Divider"下拉列表更改为所需的任何分频器设置。 我会仔细检查 ADC EVM 原理图、以确保更改正确的 LMK 时钟输出。

此致!

埃里克·克莱克纳