在这个组件上我们有一个非常具有挑战性的过零问题。

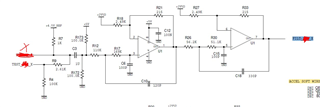

请在下方查看原理图屏幕截图、

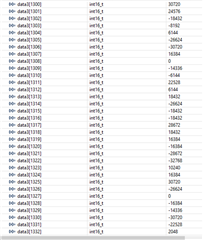

整个电路就像3轴加速计>偏移(电平上升 tp 2.5V Vref)和滤波级> ADS8345 (由5V 供电)>电平转换器(降级 IT 3V3)> FPGA > DSP (F2812)。

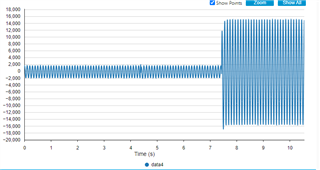

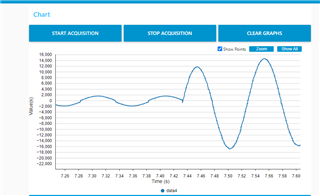

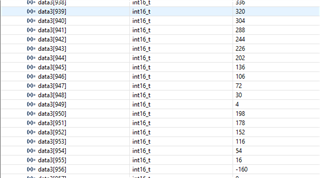

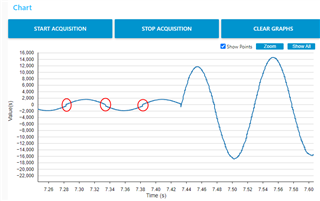

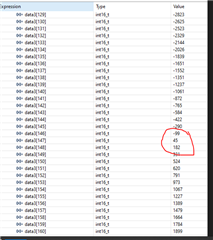

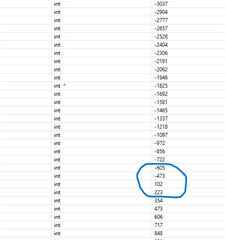

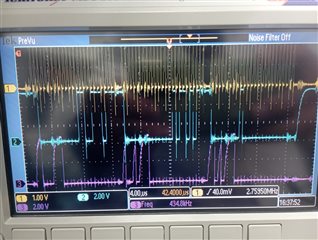

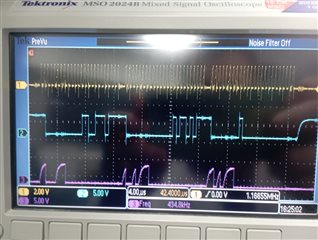

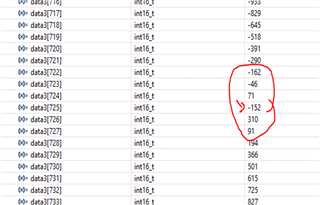

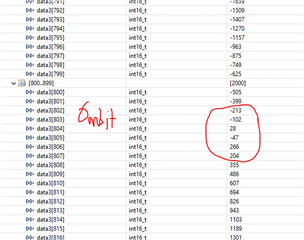

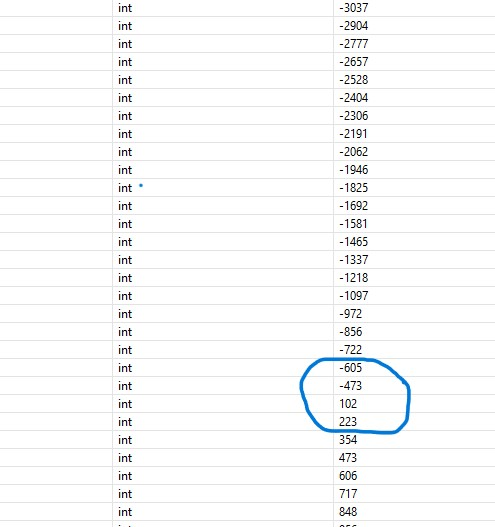

我们在 DSP 处使用数据、并且输入值在过零点有毛刺、如图所示。

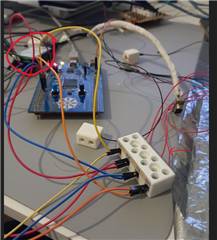

我们使用了带 STM32评估板的 ADS8345EVM 来了解问题是否与 IC 有关且结果没问题、没有干扰、我分离了 FGPA (已擦除其中的固件) 接着、将一些电线从 ADC 输入通道和 SPI 线路延伸到 STM32评估板、然后我使用 ADS8345EVM 上运行的相同代码进行控制。

SPI_TX.u8reg.S = 1;

SPI_TX.u8reg.A2 = 1;

SPI_TX.u8reg.A1 = 0;

SPI_TX.u8reg.A0 = 0;

SPI_TX.u8reg.res = 0;

SPI_TX.u8reg.SGL_DIF = 1;

SPI_TX.u8reg.PD1 = 1;

SPI_TX.u8reg.PD0 = 0;

问题仍然存在!! :/任何反馈,帮助是受欢迎的。

谢谢

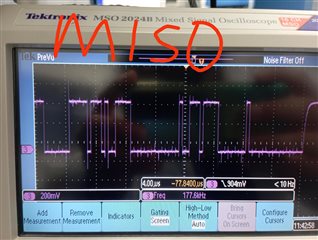

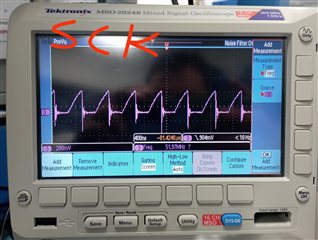

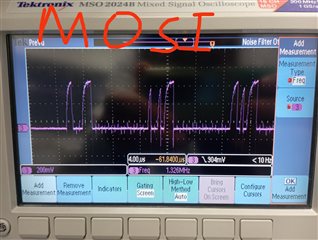

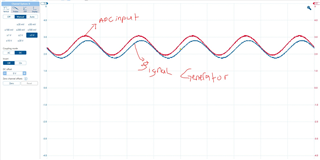

信号从输入端发送、在 ADC 通道上看到。

上次编辑:

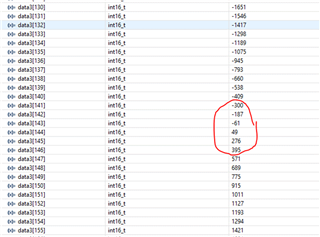

如果我没有遗漏任何东西、我还意识到毛刺脉冲行为高度依赖于信号振幅、请参阅下面的屏幕截图。

这是什么原因呢? 我是否应该使用内插?