主题中讨论的其他器件: LMK04828

您好 TI

我对 DAC37J82上的共模和差模输入电平有疑问、

该数据表指出、

- VCOM = 0.5V

- Vidpp = 400至800mVp2p

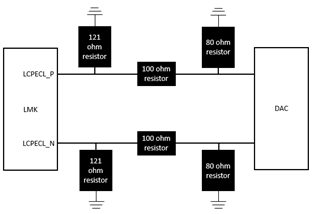

EVM 电路板上的 DAC SYSREF 终端为

- 200 Ohm 至接地

- 100 Ω 串联电阻+ 100 Ω 并联电阻(分压器)

这个设置的 IBIS 模型模拟提供了一个200mV 差动 p2p 信号、且 P/N 电平处于850mV 和1005mV、

这违反了数据表中的 Vcom 和最小输入差分电压规格。

问题

- SYSREF 的最小 DIFF 输入电压是多少

- 可接受的 Vcom 为1V +/- 200mV

是否应更改直流耦合 SYSREF 终端以使其与数据表中的 SYSREF 规范更加匹配?

请告知

谢谢

皮埃特