在我们的应用中、我们将使用 DAC3484组件、该组件的功能是生成一个频率为4kHz 且具有单边带调制的334.7MHz 频载波。 到 DAC 的输入时钟(DACCLK)的频率为1229.5MHz。

为了生成334.7MHz 载波、DAC 由以下寄存器序列进行配置:

ADDR 数据

0 => x"0000"和 x"089C"、-- 16x 内插器;fifo_ENA;alarm_out_ena;alarm_out_pol; clkdiv_sync_ENA;

1 => x"0001"和 x"050E"、-偶校验;WORD_PEACY_ENA;QUAD_ENA;ALARM_2AWAY_ENA; ALARM_1AWAY_ENA;ALARM_COILLING_ENA;

2 => x"0002"和 x"8052"、-- 16bit_in;Mixer_ENA;NCO_ENA;twos

3 => x"0003"和 x"F000",--缺省值

4 => x"0007"和 x"D9E7"、-- alarm_fifo_collection;alarm_dacclk_gone;alarm_dataclk_gone;alarm_rcity; alarm_lpage;

5 => x"0008"和 x"0000",--缺省值

6 => x"0009"和 x"8000"、--默认值

7 => x"000a"和 x"0000",--缺省值

8 => x"000b"和 x"0000"、--缺省值

9=> x"000c"和 x"0400",--缺省值

10 => x"000d"和 x"0400",--缺省值

11 => x"000E"和 x"0400",--缺省值

12 => x"000f"和 x"0400",--缺省值

13 => x"0010"和 x"0000"、--缺省值

14 => x"0011"和 x"0000"、--默认值

15 => x"0012"和 x"0000"、--缺省值

16 => x"0013"和 x"0000"、--缺省值

17 => x"0014"和 x"8000"、-- AB NCO 频率值= PHASE_addAB (15:0)

18 => x"0015"和 x"45B0"、-- AB NCO 频率值= PHASE_addAB (31:16);

19 => x"0016"和 x"8000"、-- CD NCO 频率值= PHASE_addCD (15:0)

20 => x"0017"和 x"45B0"、-- CD NCO 频率值= PHASE_addCD (31:16)

21 => x"0018"和 x"280F"、-- PLL_ndivsync_ENA、PLL 被绕过。

22 => x"0019"和 x"0840"、-- pll_m (7:0);pll_n (3:0)

23 => x"001A"和 x"0020"、--默认值

24 => x"001B"和 x"0800"、-- FUSE_SLEEP:必须设置为‘1"才能正常运行

25 => x"001C"和 x"0000",--保留工厂使用。 默认值:0x0000

26 => x"001D"和 x"0000"、--保留工厂使用。 默认值:0x0000

27 => x"001E"和 x"9999"、-- syncsel_qmoffsetAB、syncsel_ qmoffsetCD、syncsel_ qmccorrAB、syncsel_ qmccorrCD =从寄存器写自动同步。

28 => x"001F"和 x"88C0"、-- syncsel_mixerAB、syncsel_ mixerCD = sif_sync、syncsel_nco = sif_sync、syncsel_dataformatter = frame、sif_sync ='0'。

29 => x"0020"和 x"1101"、-- syncsel_fifoin = sync;syncsel_fifoout = sync;

30 => x"001F"和 x"88C2"、-- syncsel_mixerAB、syncsel_ mixerCD = sif_sync、syncsel_nco = sif_sync、syncsel_datagenerator = frame、sif_sync ="1"。

31 => x"001F"和 x"88C0"、-- syncsel_mixerAB、syncsel_ mixerCD = sif_sync、syncsel_nco = sif_sync、syncsel_dataformatter = frame、sif_sync ='0'。

32 => x"0005"和 x"0000",--重置所有报警。

数据驱动至 DATACLKp/n 线路上的16MHz、数据速率为 DACCLK/16=1229.8/DAC。

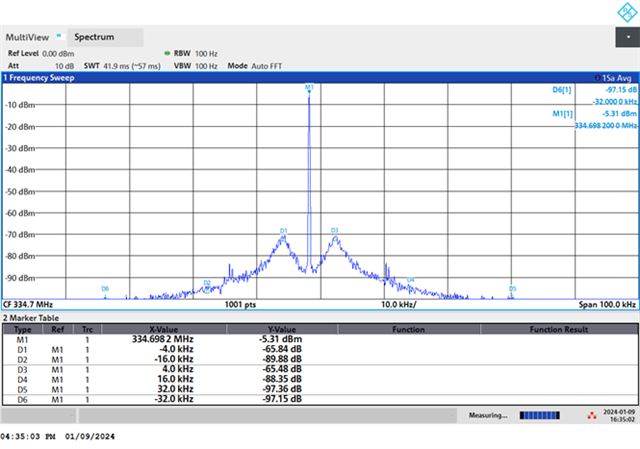

当我们提供恒定信号(CW)时、DAC 有以下频谱输出。

4kHz 和4kHz 音调是由 DAC 的输入时钟决定的。

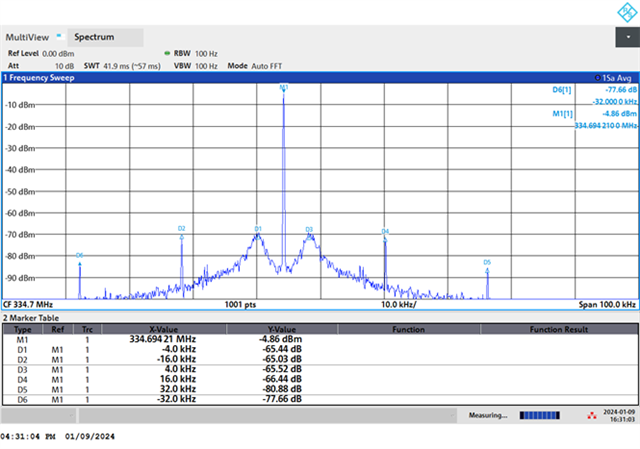

当我们为 4 kHz 信号要具有载波的频移、我们有以下频谱:

从图中我们可以观察到一些不需要的音调。 具体而言、我们观察到音调 D2 (- 16KHz =- 4x4KHz )、D4 ( 16kHz = 4 × 4KHz )、D5 ( 32KHz=8x4KHz )和 D6 (- 32KHz =-8x4KHz )。

通过增加调制频率、可以观察到不需要的音调、从而改变强度。 特别是、杂散音调的强度似乎会随着频率偏移的增加而降低。

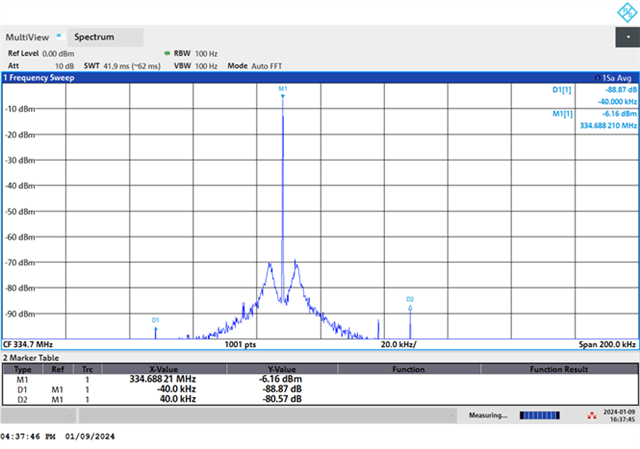

在下图中、我们拥有10kHz 调制信号的频谱。

杂散音调32KHz = 4x10KHz 和-32KHz =- 4x10KHz 远低于之前的4kHz 频移情况。

是否有任何技巧可以避免上述杂散音调?

安东尼奥