Other Parts Discussed in Thread: ADC128S022

大家好、

我明白 ADD [2,1,0]决定了哪个输入 CH。

在计时图中、 DOUT 似乎在决定所有 ADD 之前启动。 如果在 SCLK 上升时序确定了 ADD[]电平。

实际上,何时确定 Add[]级别?

此致。

转至

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADC128S022

大家好、

我明白 ADD [2,1,0]决定了哪个输入 CH。

在计时图中、 DOUT 似乎在决定所有 ADD 之前启动。 如果在 SCLK 上升时序确定了 ADD[]电平。

实际上,何时确定 Add[]级别?

此致。

转至

尊敬的 Goto-San:

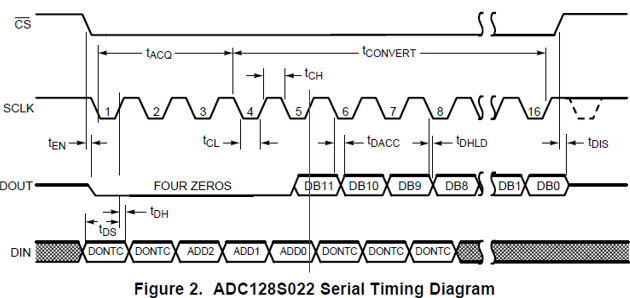

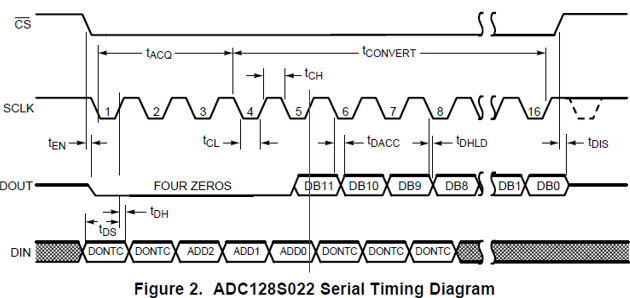

感谢您的联系。 ADD [ 2、1、0]实际上将改变下一个转换周期的输入通道。 下面是数据表第7.3.1节(串行接口)中的一些信息。 "当一个转换正在进行时、下一个转换输入的地址通过 CS 下降后 SCLK 前8个上升沿上的 DIN 引脚计时到控制寄存器中。"

请注意、上电后的第一次转换将从 IN0获取数据。 希望这对您有所帮助、如果您还有任何问题、请联系我们!

此致!

乔尔

尊敬的 Goto-San:

由于 DIN 在上升沿计时、DOUT 在下降沿计时、因此包含当前转换(D11)数据的第一个位在 ADD0读入控制寄存器时不会发出、 但即使如此、DOUT 仍然是当前转换的数据、而且我们只关心 ADD2、ADD1和 ADD0的8个 DIN 位将在下一转换周期而不是当前周期存储在 ADC128S022的控制寄存器中。

例如、在加电后的第一个转换周期(需要16个 SCLK 周期)之前、控制寄存器被设置为全0、因此第一次转换将从 IN0读取。 如果您不是从 IN0读取、则可以丢弃此读数、但如果您确实希望将 IN0用作输入之一、则它应该有效。 如果在第一个转换周期内、您将 Add[2、1、0]设置为001、则只有在 下一个 转换周期前、您将看到这一变化、也就是说、更改的 DIN 将在当前转换的 DOUT 完成后生效。

简而言之、在 SCLK 的第5个上升沿、当前转换周期(N)的 DOUT 保持在 SCLK 的下降沿被读取、而 DIN 中的 ADD0正在读取到控制寄存器中、以修改下一转换周期(N+1)的输入通道。 请告诉我、这是否有助于进一步澄清此问题。

此致!

乔尔