尊敬的技术支持团队:

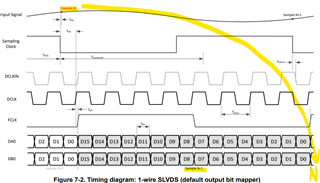

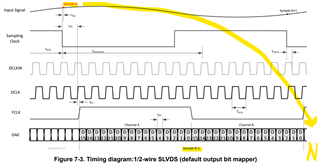

ADC3661的 SLVDS 具有2线、1线、1/2线输出模式。

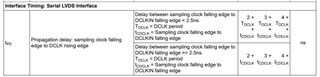

根据每个时序图、 从采样到数字数据的以下输出时序是否正确?

对于采样时钟、10MSPS = 0.1us。

2线制⇒(0.1us +TPD+TCD)* 2 (从采样到输出)

从采样到输出的1线、1/2线⇒0.1us+TPD+TCD

此致、

TTD

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Drew:

感谢您的答复。

我了解您提到的不带 DDC 的输出计时。

我想确认 10MSPS 和16位的时钟频率。

如果我有误解、可以修复吗?

2线制⇒5MHz、DCLKIN 和 DCLK = 40MHz、DA0/DA1和 DB0/DB1 80MHz (80Mbps)

1线制 ⇒10MHz、DCLKIN 和 DCLK = 80MHz、DA0和 DB0 160MHz (160Mbps)

1/2线制 ⇒10MHz、DCLKIN 且 DCLK = 160MHz、DA0 320MHz (320MBPS)

此致、

TTD