主题中讨论的其他器件:LMK00304、 LMX2594、 LMK04828

您好!

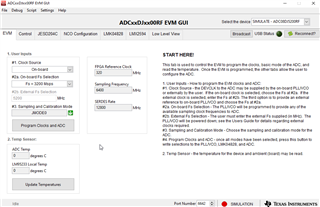

一些相关的 EVM 配置信息:

我们将使用外部参考时钟选项并相应地配置硬件。

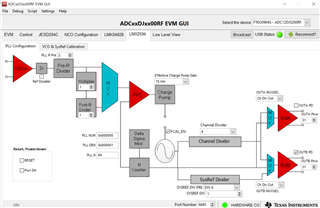

我们有一个信号发生器为 LMK00304芯片提供400 MHz @ 6dBm、用于将 LMX2594和 CLKin1作为 Fosc 提供的400 MHz 信号复制到 LMK04828B。

LMK04828正在按预期向 FPGA 输出时钟:

- DCLKout0上的200 MHz LVDS

- SDCLKout1上的10 MHz LVDS SYSREF

- DCLKout12上的200 MHz LVDS、FPGA 内部生成为320 MHz JESD 内核时钟

LMX 配置为从 RFoutA 输出3200 MHz 时钟信号、并确认已锁定:回读寄存器0x6E (R110)时、我们将读取0x4A8、这也表示校准发生在右侧 VCO_SEL 上。

LMK04828正在将 SDCLKout13上的10 MHz SYSREF 传递到 LMX 的 SYSREFREQ 引脚、LMK04828在中继器模式下启用了 SYSREF、但 RFoutB 输出当前已断电、不向 ADC 提供任何 SYSREF。

ADC 的配置遵循数据表第8.3节中详述的初始化设置程序:

0x00000080、//软复位-3

0x00020000、// JESD_EN = 0 ->禁用 JESD 收发器- 4

0x00006100、// CAL_EN = 0 ->禁用校准- 5

0x00020100、// JMODE = 0 (单通道、8通道)- 6

0x00020207、// KM1 = 7 => K = 8 - 7

0x00020301、// JSYNC_N

0x00020403、//启用8B/10B 模式和带符号2补码的扰频器- 8

0x00006101、// CAL_EN = 1 ->启用校准- 10

0x00020505、//测试模式:传输

0x00020702、// FCHAR K28.5

0x00020001、// JESD_EN = 1 ->启用 JESD 收发器- 12

0x00006C00、// CAL_SOFT_TRIG = 0 - 14

0x00006C01 // CAL_SOFT_TRIG = 1 ->启用校准- 15

结果:

在 EVM 上、我们配置了 LMK、LMX、然后是 ADC 本身。 然后 读取 ADC 的 JESD 状态寄存器0x208,检查 PLL 锁定状态--它返回0!

我在这里寻求有关 解决此问题的步骤的建议、以便 ADC PLL 可以锁定、然后我们可以继续查看 JESD 链路开启。

提前感谢!