请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS1114-Q1 如果在 AIN0-AIN3上施加5伏的电压 使 VDD 为3.3V,模拟输入通道将会损坏? 问这个问题的原因是允许的最大 VDD 为7V、因此无论 VDD 如何、所有 AIN 引脚都应具有7V 的容差?

提前感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

如果在 AIN0-AIN3上施加5伏的电压 使 VDD 为3.3V,模拟输入通道将会损坏? 问这个问题的原因是允许的最大 VDD 为7V、因此无论 VDD 如何、所有 AIN 引脚都应具有7V 的容差?

提前感谢。

尊敬的 Rohan:

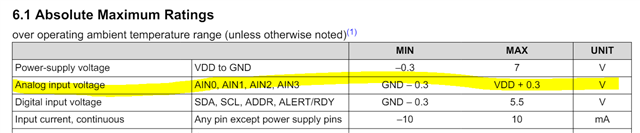

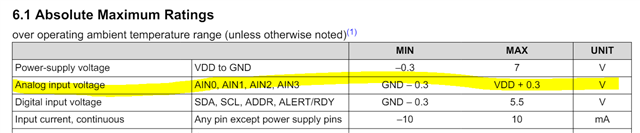

绝对最大模拟输入电压取决于 VDD 电源。

如果 VDD = 5V、最大输入电压不应超过5.3V

如果 VDD = 3.3V、最大输入电压不应超过3.6V

任何更高的值都可能会损坏器件。

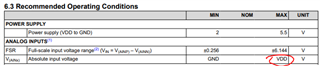

请记住、这是绝对最大值。 对于建议的工作条件、输入电压应介于 GND 和 VDD 之间:

ADC 无法测量高于 VDD 的电压。

如果输入引脚上的电压高于 VDD、那么 ADC 将输出对应于 FSR (7FFFh)的代码或对应于 VDD 的输出代码(如果 FSR 设置较高(即 VDD = 5V 且 FSR =±6.144V)。

此致、

天使