您好!

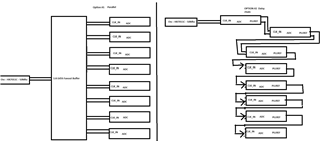

我打算设计一个将 x8 ADCQJ1600器件连接到 FPGA 的电路板-每个 ADC 都通过四个

差分信道(12位64/66B JMODE 8)。 ADC 采样率为1GHz。

我的问题是:

1.更好的选择是- A 将 主时钟振荡器输入到第一个 ADC、然后 将 PLLREF 连接(菊花链) 从一个器件输出到下一个器件? (与 TWS12qj1600 EVAL 板中一样)。

b :要通过诸如 ZL40218之类的精密1:8 LVDS 扇出缓冲器将时钟振荡器并联至八个 ADC、

c:从时钟振荡器驱动第一个 ADC 时钟输入、然后通过 精密1:8 LVDS 扇出缓冲器从第一个 ADC 中驱动另外七个。

输入时钟振荡器抖动的规范是什么?

3. HX7011C - 50MHz 时钟振荡器是否正常?

此致、

乔拉