大家好、

在与 CPU 进行 SPI 通信时、以下引脚是否需要上拉/下拉?

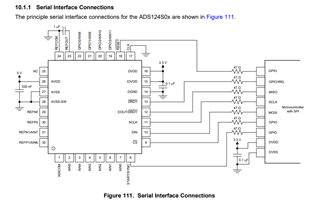

数据表中的图111中没有上拉/下拉电阻。

如果需要、请告诉我建议的电阻值。

SCLK

CS

DIN

DOUT

DRDY

开始

复位

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的高桥敦志:

基本上不应允许任何数字 CMOS 输入引脚悬空、因为这可能导致在 NMOS 和 PMOS 晶体管都可能处于导通状态的过渡区中产生过大的电流。 数据表第6节中的引脚功能表指示了哪些引脚是输入和输出。

至于引脚连接本身、关于引脚连接方式没有统一的答案。 如果引脚是被驱动的输出、则不需要上拉或下拉电阻器。 上拉和下拉电阻器值将取决于您希望上拉或下拉的强度。 这可以在10k (强)至100k (弱)欧姆范围内。 在某些情况下、该引脚可直接连接到 IOVDD 或 DGND。

SCLK -该引脚来自 MICRO 并是输出引脚、因此无需上拉或下拉

CS -此引脚连接将取决于具体用例。 如果 CS 始终保持低电平、则可以直接连接到 DGND 或通过下拉电阻器、否则连接到微控制器的输出。

DIN -此引脚来自 MICRO、因此无需上拉或下拉

DOUT -此引脚是 ADS124S08的输出引脚。 仅当 CS 处于低电平时、该引脚才会处于驱动状态。 对于该引脚、状态由微输入决定。

DRDY -这是一个始终有效的推挽输出引脚、不需要上拉或下拉电阻。

START -如果使用命令而不是引脚进行转换控制、则可以直接将此引脚连接到 DGND

复位-如果不使用此引脚、则可以直接将其连接到 IOVDD。 此引脚可以直接连接到微 GPIO 或通过上拉连接。

如需更多信息、请参阅 ADS124S08数据表中的第10.1.5节。

此致、

鲍勃 B