您好!

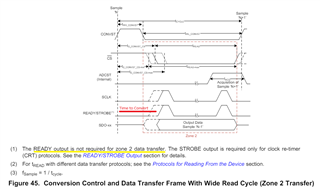

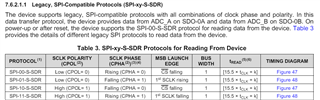

我正在使用 ADS9224 ADC、并且对区域2的接口和时序有疑问。 是否为区域2定义了3兆采样/秒速率? T_DRDY = 315ns 必须是最大转换时间。 在区域2、我们始终读取前一个样本。 因此、在当前数据传输结束时、来自前一次转换的数据可用于接下来的315ns。 该字段即使在我们使 CONVST 线路有效之前也应该可用(我们使 CONVST 有效的次数不能超过每333ns)。 我的猜测是在区域2期间 CONVST 有效会导致缓冲区从内部 ADC 寄存器复制到 SPI 输出缓冲区、这需要的时间达 TD_CONVST_CS (min)=15ns。 这些假设是否正确? 另外、根据区域2传输的最佳性能说明、[TD_CONVST_CS + TREATE]必须保持在150ns 以下。 为什么150ns 是限值、而不是接近333ns? [TD_CONVST_CS + TREATE]的最长时间是多少?