Other Parts Discussed in Thread: ADS8681

尊敬的 TI:

以下报告显示了 ADS8681器件存在的问题。 我们希望就此问题与 FAE 联系、或从对此部件有经验的人员那里获得有关潜在原因的提示。 谢谢!

执行摘要

本报告详细介绍了在不同电路板上的几个 ADC 中观察到的间歇性错误读数。 本报告使用先进的诊断技术分析了该问题、包括在200MHz 进行基于 FPGA 的信号采样和使用逻辑分析仪进行实时信号监控。 关键的是、这些有故障的 ADC 样本会导致控制器行为出现严重故障、从而可能影响系统的稳定性和性能。 这突出了解决这些异常问题以防止操作故障的紧迫性。

简介

ADC 出现了零星的故障、特点是单次采样读数不正确。 最初的假设重点在于双 SPI 模式和单 SPI 模式下的 SPI 通信误差。 除了初步评估、本报告还探讨了硬件级信号完整性和采样策略。

问题说明

尽管 SPI 通信模式和时钟速度发生变化、但错误的 ADC 读数仍然存在、这表明可能存在内部 ADC 故障或外部信号完整性问题。

方法和材料

FPGA 采样: 利用 FPGA 以200MHz 的高频对 ADC 输入信号进行采样、以捕获详细的信号行为。

逻辑分析仪: 将采样信号重定向到逻辑分析仪以进行广泛的实时分析、有助于深入了解 ADC 数据输出的时序和完整性。

SPI 模式变化: 在不同的时钟设置下测试了双 SPI 和单 SPI 模式(特别是在12.5MHz 模式下)以评估对 ADC 性能的影响。

信号完整性分析: 对信号路径、电压电平和接地进行全面检查、以确定导致信号衰减的所有因素。

观察结果

探测无影响: 已确认监控设置(包括探针连接和信号重定向)不会改变或干扰 ADC 操作。

各个设置中的持续错误: 错误的发生在不同的工作模式和设置中保持一致、从而强化了问题可能来自 ADC 或其直接信号环境的概念。

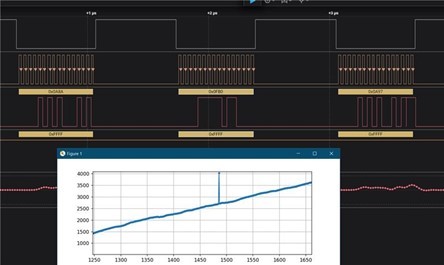

图1:25 MHz SPI 时钟上的错误采样

下图说明了在 SPI 时钟设置为12.5MHz 时捕获的故障采样。 它显示来自逻辑分析仪的输入数据、该分析仪以每秒5亿个样本的速率进行记录。 该图显示了 MISO-0线路的模拟信号、表现出活动。 相比之下、MISO-1线始终保持高水平、没有变化或活性。 这种可视化表示有助于理解信号的动态特性并识别误差的时序。

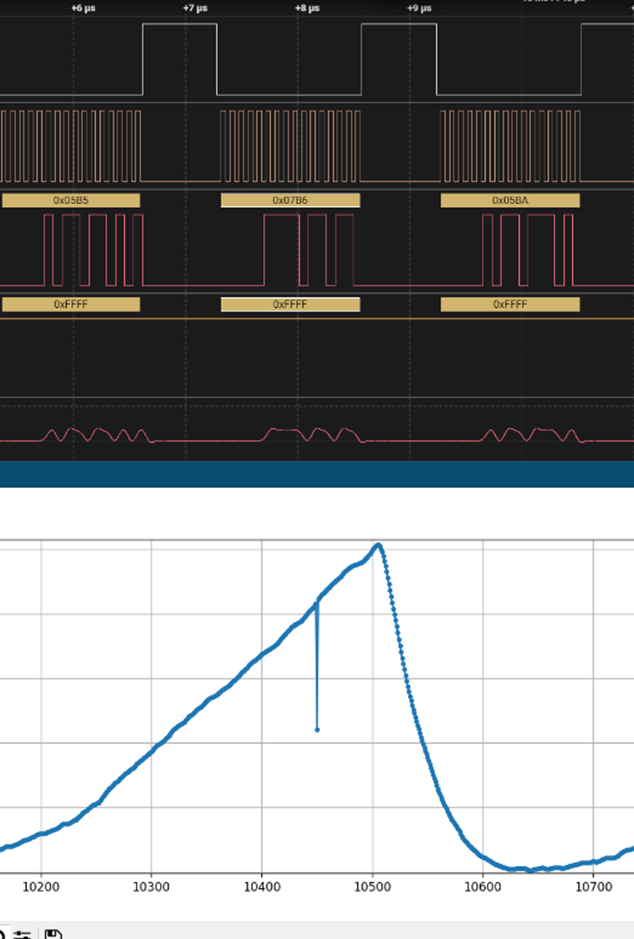

图2:12.5 MHz SPI 时钟上的错误采样

讨论

分析表明、ADC 误差不太可能是由于 SPI 通信故障造成的、而更可能与内部 ADC 误差或外部信号干扰有关。 鉴于高分辨率采样和实时分析能力、研究结果强烈表明、ADC 在某些情况下会受到固有的 ADC 降低、但在 ADC 设计或制造过程中可能会被忽略。

结论

本报告中记录的调查证实了 ADS8681的间歇性和错误读数、此类读数在严重影响控制器运行和整体系统可靠性。 这些故障不仅具有破坏性、而且如果不及时解决、可能导致严重的操作故障。