主题中讨论的其他器件: ADS1274

工具与软件:

您好!

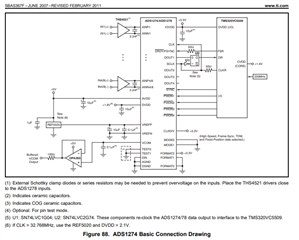

ADS1278数据表的图88在第38页显示了给定的原理图:

我看到有一个连接到 ADS1274的 DOUT1和 SCLK 的触发器。 这是 D 触发器吗? 该触发器的用途是什么? 如果我想在低于27 MHz 的 CLK 频率下使用 SPI 通信方法、这款触发器是否必不可少?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Rahul:

欢迎来到 TI E2E 社区。

包含触发器是为了满足某些 MCU/DSP 的时序要求。 限制是 SCLK 传播延迟 T-DOPD。 如果您使用27MHz 13.5MHz 和 CLK=SCLK=SCLK ,那么您将不需要这个触发器。 ADS1278会在 SCLK 下降沿启动数据、主机 MCU 通常会在 SCLK 上升沿捕获数据。 只要传播延迟小于1/2*t-SCLK,就可以满足时序要求。

假设 IOVDD 小于3.15V、则最大 T-DOPD 为32ns。 这会将最大 SCLK 频率限制为15.6MHz。

请查看此 e2e 文章、其中更详细地介绍了这一点:

您还可以配置 SPI 端口、以在 SCLK 的下降沿捕获数据。 在本例中、最短保持时间为10ns。 该模式允许在不使用触发器的情况下实现27MHz 的最大 SCLK。

此致、

N·基思

精密 ADC 应用