主题中讨论的其他器件: DAC39J82

工具与软件:

您好、TI 支持团队:

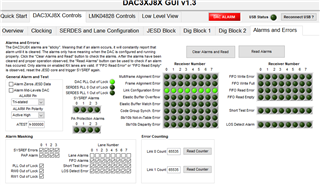

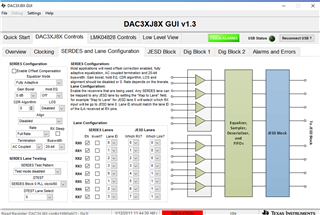

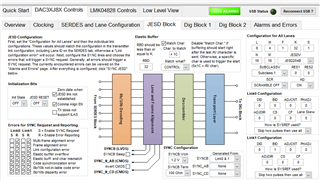

在 DAC3XJ8X GUI 中、我们会看到 链路配置错误。

我们当前的固件方案如下:

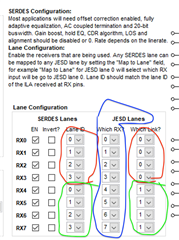

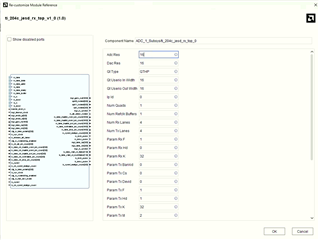

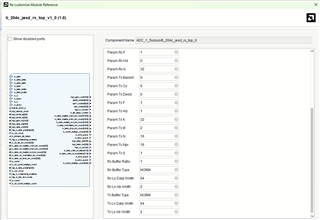

我们使用两个 TI JESD204内核、每个 ADC 一个(每个 ADC 4个 RX 通道)、对于 DAC 所需的全部8个通道、我们使用每个 IP 内核的4个 TX 通道。

目前、我们的 ADC 运行良好、FPGA 端和 ADC/DAC 端的 GBT 都成功锁定、但始终存在"链路配置错误"。

是否可以使用两个单独的 TI IP 内核来运行 DAC? 现在设置为 LMFS=8411、K=32。

我们是否需要仅对 DAC 使用单核?

谢谢!

Ryan