工具与软件:

嗨、团队:

在继续模式读取中使用 ADS1255 ADC 时存在问题。

ADS1255的 fclk 为8MHz、在30Ksps 继续模式下运行。

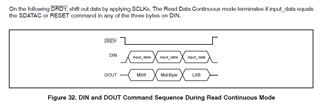

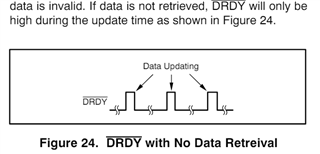

SPI 读出程序将 DRDY 信号下降沿引用为读出3字节数据。

但是、在我们的测试中读数会随机出错。

主器件 SPI 是 Tiva SSI 驱动程序代码、我们也测量了 SPI 波形、看上去一切正常。

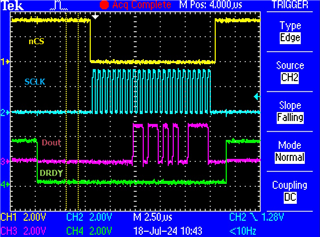

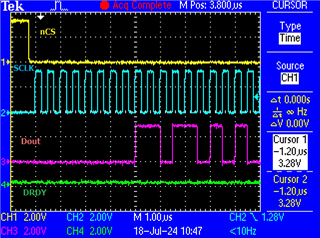

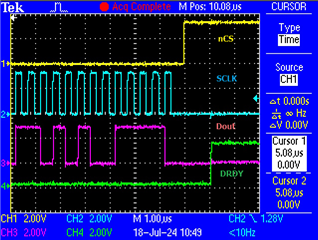

下图是我们捕获的错误读数。

读出的典型错误看起来像是重复读取的 MSB 字节、并导致24位(3字节)数据错误。

例如:AA BB XX 是 相邻值。

可能喜欢 AA AA BB。

另一个错误情况是复制的中间字节、如 AA BB BB BB。

虽然我们尝试过一些、但该错误仍然是随机发生的。

1.减少到15K SPS

2.调整 SPI 时钟速率(2MHz ~ 1.6MHz)

我们认为 SPI 读取时序在正确/错误的情况下没有差异、并且应满足 ADS1255规范。

我们认为 fclk 8MHz 和工作设置30Ksps 仍应符合规范。

问题可能是什么、是否有任何暗示?

此致、

Paul