工具与软件:

尊敬的社区:

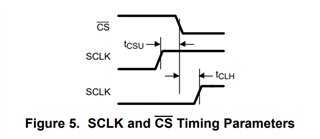

在分析数据表中的串行时序图时、我无法确定 CPOL 和 CPHA 的值。 您能否说明一下它们是什么? 此外、在第5页(注释2)中指出:"只要严格遵守设置和保持时间 tCSU 和 tCLH、当 CS 置为有效时、时钟就可能为高电平或低电平。" 这是否意味着我可以对 CPOL 使用两个不同的值?

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的社区:

在分析数据表中的串行时序图时、我无法确定 CPOL 和 CPHA 的值。 您能否说明一下它们是什么? 此外、在第5页(注释2)中指出:"只要严格遵守设置和保持时间 tCSU 和 tCLH、当 CS 置为有效时、时钟就可能为高电平或低电平。" 这是否意味着我可以对 CPOL 使用两个不同的值?

谢谢你。

路易吉、您好!

数据在 SCLK 下降沿通过 DOUT 按时钟输出。 这意味着数据对于控制器在 SCLK 的上升沿进行采样是有效的。 该器件有两种有效的可能:SPI 模式3 (CPOL = 1、CPHA = 1)和 SPI 模式0 (CPOL = 0、CPHA = 0)。

SPI 模式3由下面的第一个 SCLK 显示、在该模式下、SCLK 在 CS 下降之前变为高电平。 在这种情况下、DOUT 的第一个位在 CS 变为低电平后 SCLK 的第一个下降沿随时钟移出、并在 SCLK 的下一个上升沿被采样。

SPI 模式0由下面的第二个 SCLK 显示。 在这里、SCLK 在 SCLK 下降沿之前保持低电平、正是在这里、CS 的下降沿随时钟输出 DOUT 的第一个位、然后该位可由控制器在下一个上升沿有效读取。

具体使用哪种模式由您决定、但我想 SPI 模式3将更易于实现 并简化时序要求。

此致、

Joel