工具与软件:

这是一款1MSPS ADC。 数据表中规定"边沿抖动"必须最大10ps

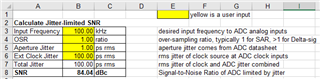

1) 1)我不确定"边缘"抖动意味着什么。 这是周期间抖动吗? 我假设它的含义如下所示。

2)为什么这是紧? 10ps 是10ppm 的1 MHz。 看起来您可以以任何自己喜欢的最高1MSPS 的速率触发 CONVST、那么该抖动为何很重要? 我甚至不知道它与 SNR 有何关系;我不确定计算是否正确、但我认为在100kHz 下保持>93dB 的 SNR 仍然只意味着100ps 抖动。

我想对 CONVST 使用硅振荡器等简单的器件、但这些器件的抖动要高得多。 如果我使用具有100 ps 抖动的时钟、实际的性能影响是什么?

关于数字输出、我还有一些其他问题、但由于这是另一个主题、因此我会 重新提出一个问题。