工具与软件:

您好、TI 专家。

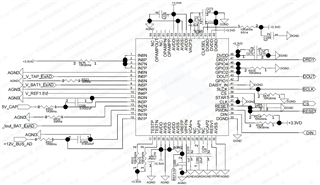

当我使用 ADS131E08收集数据时,我返回的数据是错误的,我使用了 RDATA 命令 。 硬件接口为电源 AVDD = 3.3V、芯片的内部时钟为2.048MHZ、单端信号通过(CH1~CH6)输入。

使用的 MCU 是 C2000 DSP280039、我的软件配置过程如下:

初始化 SPI、4MHz、16位、极性0、相位0;

;手动11.1上电时序复位 ADS131e08

3.发送 SDATAC 命令和发送 STOP 命令;

4. Confg1 0xd2h、多数据回读模式、 采样率16ksps;

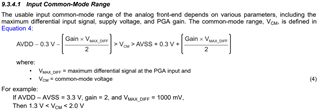

5、Confg3 0x40h、使用外部基准源(3V);

用于配置0x10h 的6~通道寄存器、其中 CH1、CH6启用且 CH7和 CH8禁用;

7、发送启动命令;

8、将 SPI 的 SCLK 频率更改为10MHz;

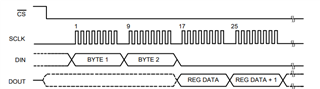

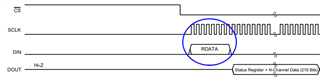

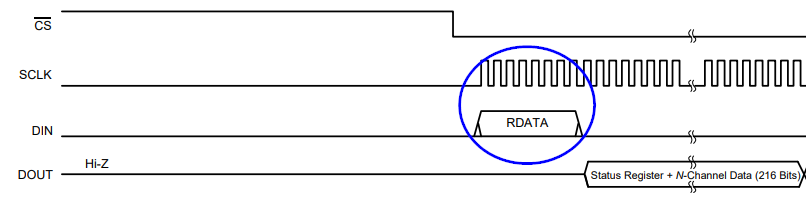

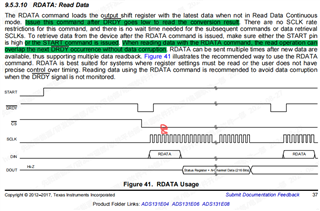

接下来、我 在15KHz EPWM 中断函数中发送了 RDATA 命令、然后发送剩余的216个 SCLK 以读取八个通道的数据。 CS 引脚在整个过程中保持低电平。 由于15K 的中断频率与 ADS131E08设定的采样频率异步、因此会出现 DRDY 事件与读取数据时钟 SCLK 重叠的现象、但手册说明这不会导致数据损坏、这可以在实际测试中看出。

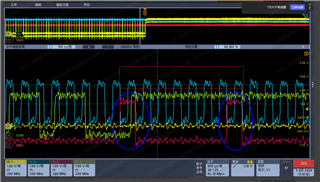

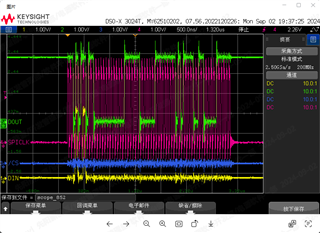

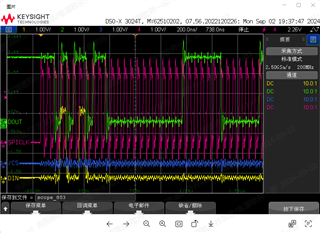

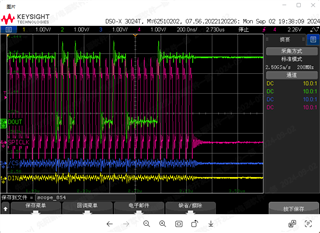

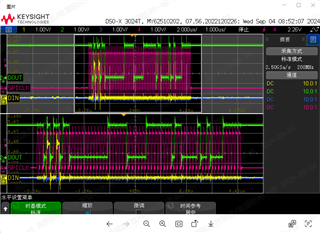

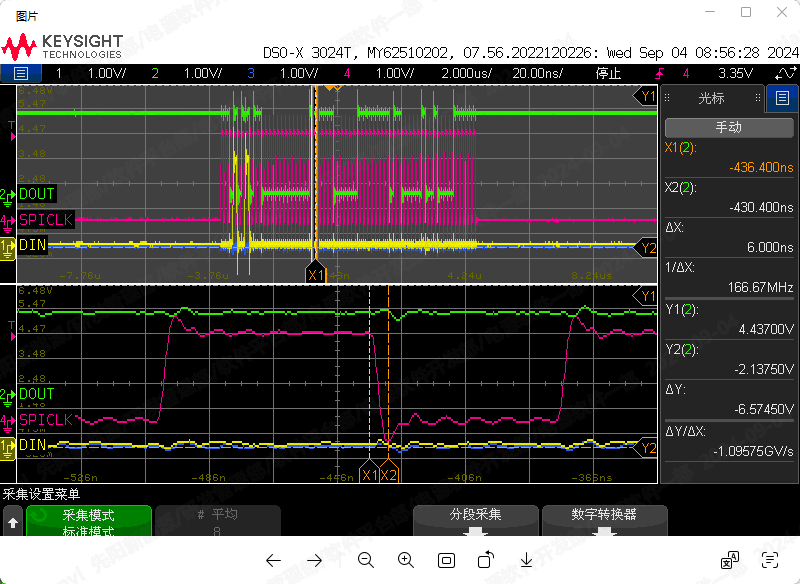

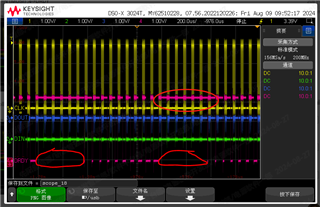

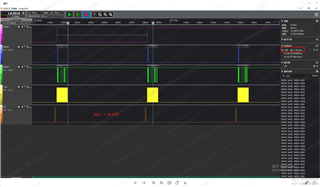

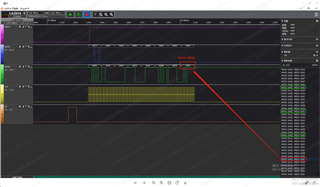

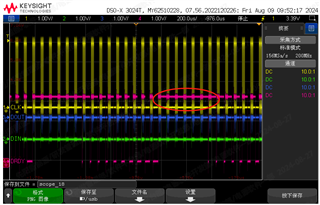

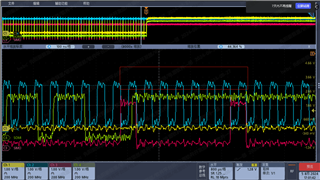

示波器波形:

1->SCLK ;2->DOUT (MISO);3->DIN (MOSI) ;4->DRDY

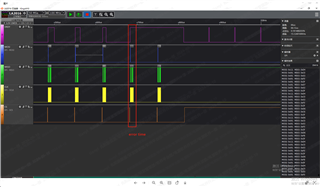

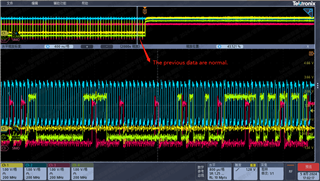

数据损坏发生在以下时间:

我们测试了相关的数据错误时间、测试方法为:

1、 仅读取通道2数据的高8位(24位数据的高8位)、因为通道2的输入约为1.5V。如果数据突然变化、高8位数据将发生变化。 它与上述配置的区别是:SPI 极性1、相位0。

2 μ s、高8位数据将发生变化、上拉 CS 引脚并捕获通过它的示波器波形。

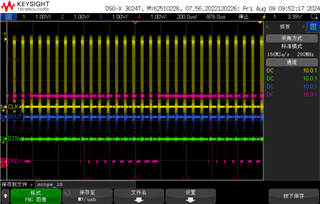

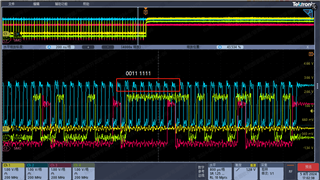

数据正常时间的波形:1:CS;2、SCLK、3;DIN (SIMO);4、DOUT (SOMI)

正常数据高8位0011111:

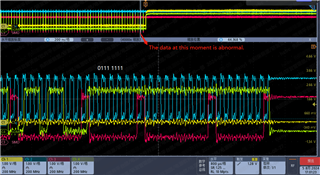

异常时间高8位数据011111:

最后、使用单个转换指令 RDATA 时、DRDY 事件是否真正影响数据读取?

我们想知道问题是什么。 期待您的回复、谢谢!