Other Parts Discussed in Thread: ADS8681

工具与软件:

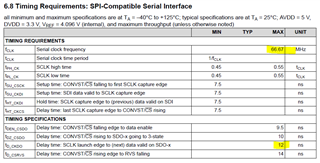

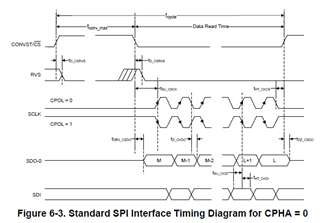

我对 ADS8681数据表中提到的参数有疑问。 在第九页(第6.8节)列出了可能的 SPI 频率与66.67 MHz 有关。 再往下看、它指出 CLK 变化和 SDO 信号更新之间的延迟可高达12ns。 根据我的计算、66 MHz 不能保证 CLK 频率、因为单个 CLK 周期约为15ns。 ADS8681引起的延迟将导致器件发送的所有数据发生位移

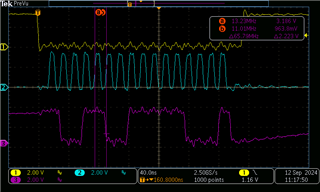

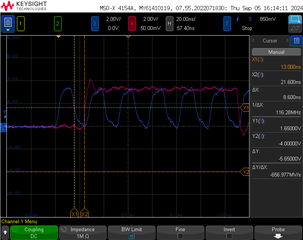

在测试过程中、我注意到8ns 到11ns 之间的延迟(在规格范围内)、但我已经在40 MHz 附近发生了位移。 我直接在芯片上测量了相似的数值。 根据我的理解、延迟是由 ADS8681产生的、而不是线路电容/电阻。 我还确保使用 SPI 模式0、并且仅将基准电压设置更改为1.25 * Vref。 如果重要、该设置由在菊花链中配置的三个 ADC 组成。

现在回答我的问题:配置中有什么我可能遗漏的东西可以帮助解决所观察到的延迟问题吗?

为达到所述的60 MHz (或甚至接近40 MHz)、建议采用哪些程序/设计?

我将感谢您的任何帮助、并感谢您的任何回答。

(蓝色:CLK、红色:SDO)