Other Parts Discussed in Thread: LMK04828, ADC12DJ5200-SP, LMX2594, LMK00304, ADC12DJ5200RF

主题中讨论的其他器件: LMX2594、 LMK00304、LMK04828、 ADC12DJ5200RF

工具与软件:

您好!

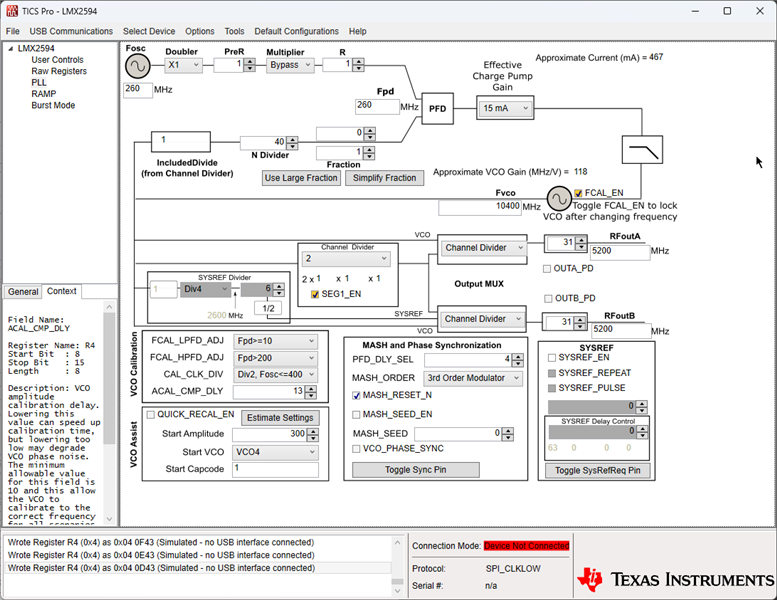

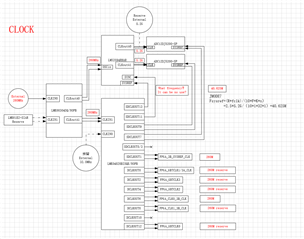

我们使用2个 ADC12DJ5200-SP、并使用时钟芯片 LMX2594RHAR 和 LMK04828BISQE/NOPB、请帮助我们了解如何实现下图中的时钟输出。

也有助于查看 ADC12DJ5200-SP 原理图、谢谢!