主题中讨论的其他器件:ADC09QJ1300EVM

工具与软件:

您好论坛

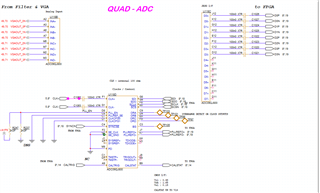

我将使用 Arria 10 FPGA 作为此 ADC 的接收器。

链路无法正常工作、并且只要我能判断同步序列未完成(基于 SYNC_N 信号保持低电平的事实)。

作为第一步、如果 TI 能验证以下初始化序列是否正确、我将不胜感激。

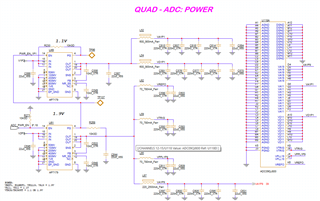

此外、我还附上了相关原理图的节选。

ADC 的输入时钟为 LVDS 100MHz。 请注意、在下面的步骤3、16和17中投票成功。

我需要的采样 F 为500MSPS。

我使用的序列为:

1.设置电源开启

2.软复位(0x80到0x0)

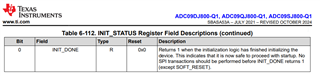

3.轮询 0x270中的位0

4. CPLL 复位(1至0x5C)

5. VCO 偏置(0x4A 至0x3F)

6. PLL (0x9至0x3D)

7. PLL (0x5至0x3E)

CPLL 无复位(0至0x5C)

JESD EN (0至0x200)

10. CAL DIS (0至0x61)

11、JMODE (2到0x201)

12. KM1 (0x1F 至0x202)

13.各种(2至0x204)

14、校准设置(1到0x62)

15、校准设置(1到0x65)

16.轮询 VCO CAL 完成、0x5E 中的轮询位0

17.轮询 CPLL 锁定、0x208中的轮询位0

18.启用 CAL 状态机(1至0x61)

19。重新启动 JESD (1至0x200)

20.完成

非常感谢

David