大家好、

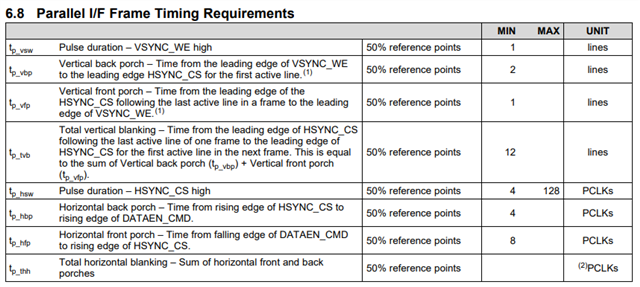

您能在下面询问我们的客户吗?

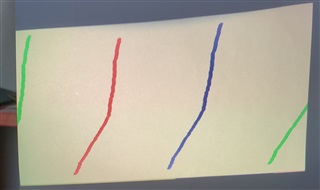

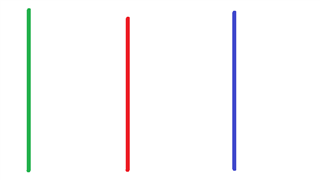

我目前正在处理一个以通过并行 RGB565接口驱动 DLPC2607为中心的应用。 在电流测试中、图像明显失真、我怀疑我违反了接口上的一个时序限制。 我尝试投影的映像为:

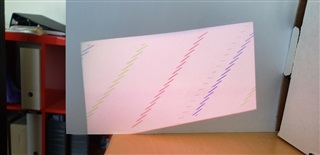

但投影仪上显示的图像为:

上图是以6.25MHz 的像素时钟速度写入 DLPC2607的。

我知道问题还与我尝试写入的文件或用于写入的实用程序有关、因此我也会联系这些供应商。 但是、如果我将像素时钟减半/加倍、情况确实会改善/恶化。 下图以3.125MHz 的像素时钟速度写入 DLPC2607:

速度与失真之间似乎存在某种相关性、我认为这个问题可能与时序有关。

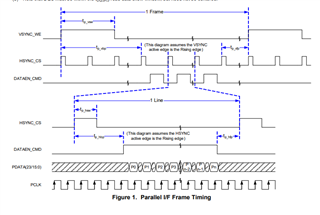

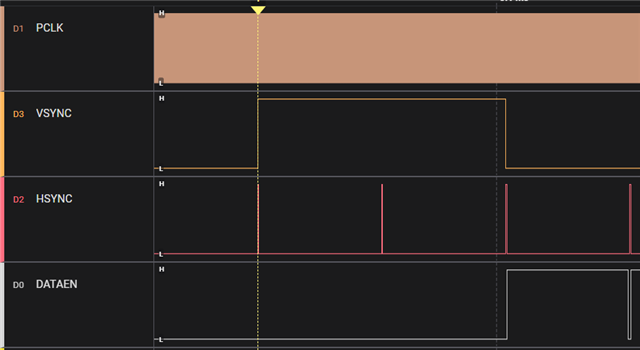

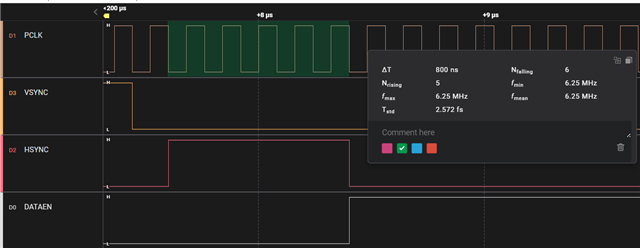

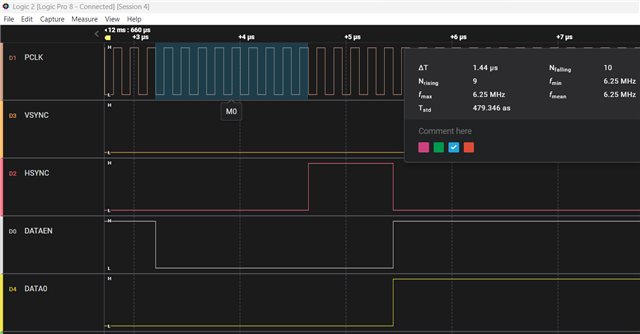

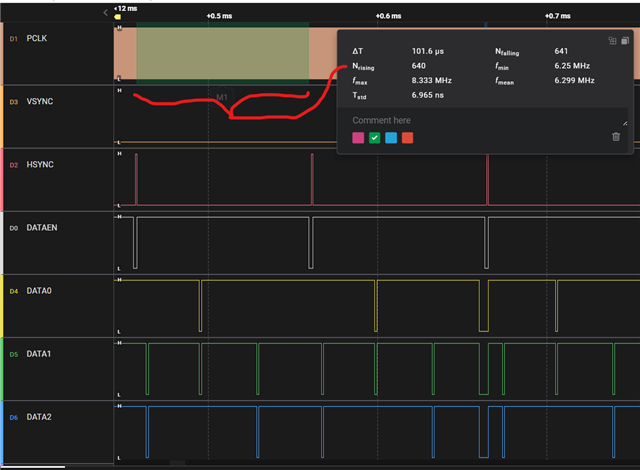

我已经连接了 PCLK、HSYNC、VSYNC、DATEN 和 D[0-3]信号的逻辑捕捉。 捕获是使用 Saleae 逻辑分析仪获取的、需要 打开 Saleae 逻辑2。

e2e.ti.com/.../parallel_5F00_RGB_5F00_capture.zip

我确实认为我满足这些规格、原因如下:

tp_vsw 和 tp_vpb:

在有效数据随时钟输出之前、VSYNC 会在2个完整线路上生效。

TP_Hsw 和 tp_hpb:

在 DATAEN 生效且数据被写入输出之前、HSYNC 会在5个上升沿生效

TP_HFP:

在 DATAEN 的下降沿和 HSYNC 的上升沿之间有9个 PCLK 周期。

此外、 每个 DATAEN 有640个上升 PCLK 边沿、即每行写入640像素:

如果您知道任何可能导致此行为的与时间有关的问题、我很感激您的了解。

此致、

Danilo.