主题中讨论的其他器件:DLP2021-Q1、、 DLPC230-Q1

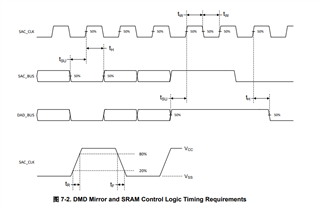

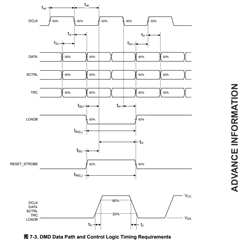

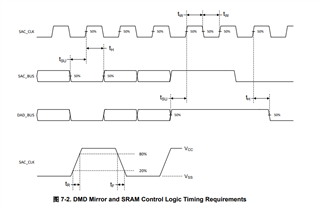

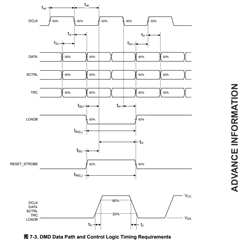

由于我要选择自己的控制器来控制 DMD、因此我想详细了解 DMD 的控制时序。根据 DLP2021-Q1文档提供的以下 DMD 时序图、我似乎不知道如何控制 DMD 显示。 我想知道 DLP2021-Q1控制是否有更详细的时序或内容吗? 非常感谢您的帮助。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

由于我要选择自己的控制器来控制 DMD、因此我想详细了解 DMD 的控制时序。根据 DLP2021-Q1文档提供的以下 DMD 时序图、我似乎不知道如何控制 DMD 显示。 我想知道 DLP2021-Q1控制是否有更详细的时序或内容吗? 非常感谢您的帮助。

您好 Cherry:

请给我们的团队一些时间来研究这个问题、因为人们会因为假期而外出。

您是否有 dlp2021leq1evm 之一? 有一个用户指南和控制程序、或许这些都是有用的信息、可以帮助您熟悉设计。

https://www.ti.com/tool/DLP2021LEQ1EVM#tech-docs

还请参阅以下有关 dlp3021q1的文档 、其中的内容与之类似、可用作参考或获得更多信息:

设计指南:

https://www.ti.com/lit/an/dlpa086/dlpa086.pdf

FPGA 指南:

https://www.ti.com/lit/pdf/dlpu100

谢谢。

亚历克斯·陈

尊敬的 Alex Chan:

在某些特殊应用中、当需要产品的结构和尺寸时、我们必须自行设计和开发 DMD 控制板。 虽然可以购买 TI 的芯片组并参考 TI 提供的 EVM 原理图、但硬件系统肯定会有一些差异、 而且、连接到 DMD 的电缆可能也不同、因此必须在首次设计和处理后调整硬件系统。 在调试过程中、可以发现大多数问题都在控制器和 DMD 之间、因为没有 DMD 接口控制协议、找不到原因和调试方法。 上述技术文档只能帮助我们调试我通过 GUI 购买的 DLP2021LEQ1EVM、以及通过我自己的器件调试 DMD 器件。 因此、我想了解 DLP2021-Q1的详细接口控制协议。

谢谢。

切里

您好 Cherry:

控制器和 DMD 之间的接口是专有的、因此我们只能提供时序图。 不能披露从控制器发送到 DMD 的数据的详细信息。 DLP2021-Q1芯片组的 FPGA 应视为 TI ASIC、我们为此仅发布经过全面测试/验证的二进制固件、其他 DMD 控制器就是这种情况。 这就是调试仅限于确保控制器到 DMD 的时序在数据表规格范围内的原因。 正如您所指出的、如果控制器和 DMD 之间存在问题、通常是由于存储器中的布局或固件损坏而导致信号完整性较差的结果。 虽然 DLP2021-Q1和 FPGA 组合并非如此、但某些 DMD 控制器包含"训练"功能、其中 DMD 向 DMD 提供反馈以指示接口状态/运行状况(即 DLPC230-Q1)。

我们将发布作为 FPGA 的替代产品的现成 MCU 控制器选项、用于支持 DLP2021-Q1 RTM。 此 MCU 控制器将提供各种主机接口和存储器接口选项。 更多详细信息将在今年晚些时候发布。