工具/软件:

您好 Evan、

我为这一个打开了一个公共线程。

(+) DP83867IR:软件复位后的异常行为-接口-内部论坛-接口-内部- TI E2E 支持论坛

因为我要休假一段时间、所以我把讨论的内容公开、让任富联络。

目前我们有两个申请:

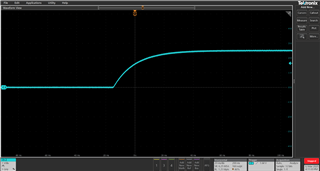

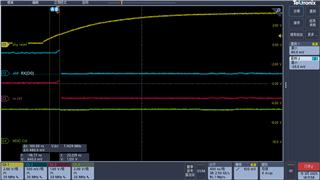

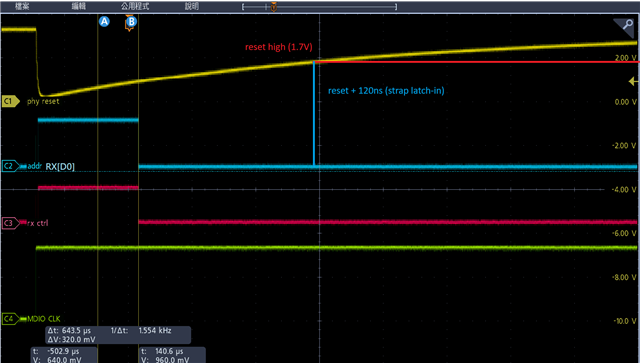

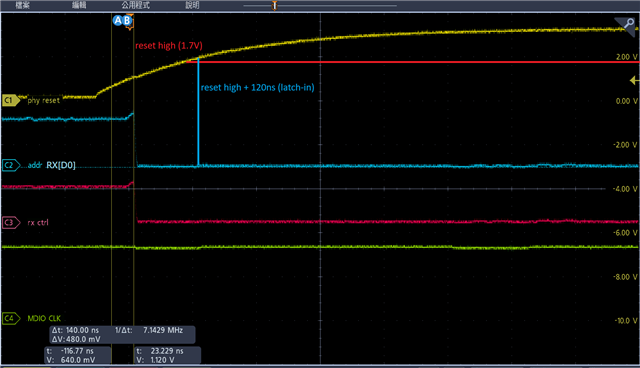

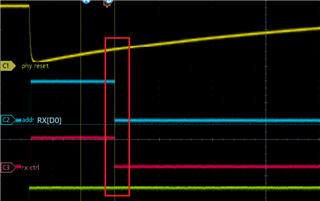

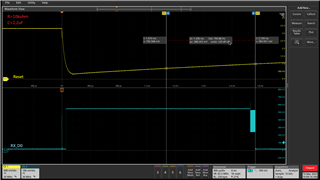

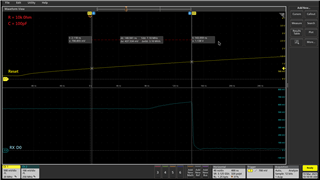

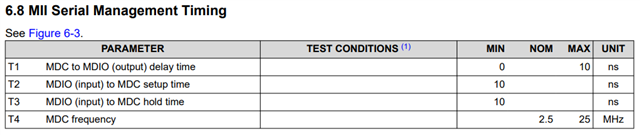

1. 我们是否得到了反馈检查上升时序规格。 与设计团队合作?

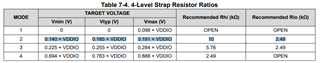

2.如果我们将 EVM 重新设计为0.1uF / 1uF、测试结果如何?

另外、对于仁孚、请您帮助解决以下两个问题:

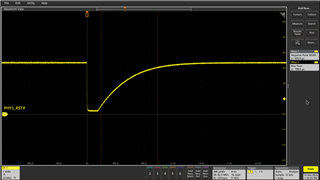

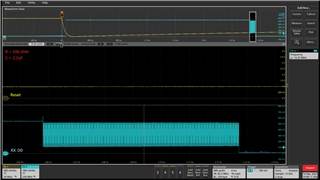

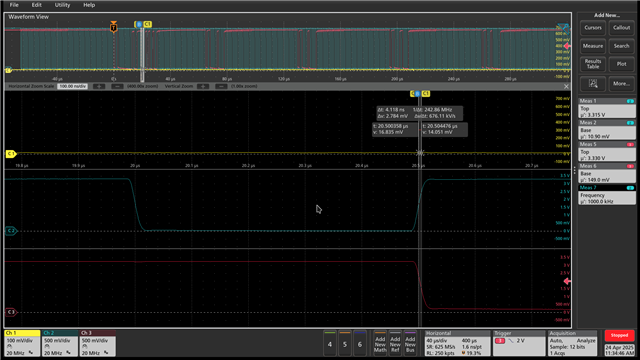

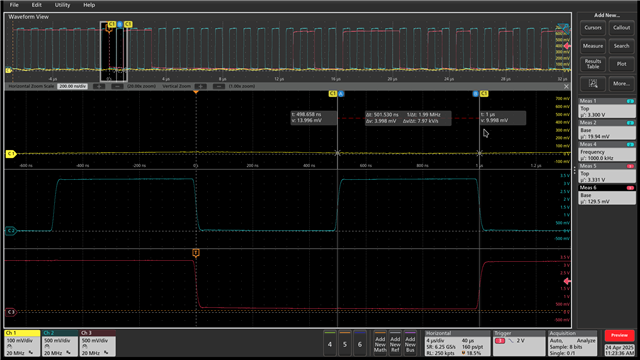

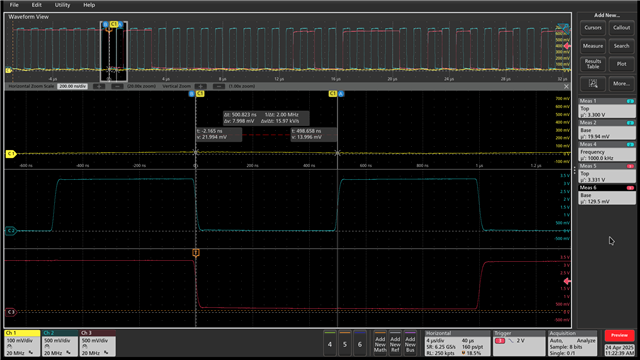

1.是否有0.1uF 的示波器?

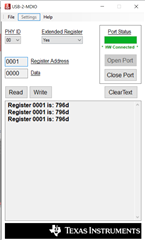

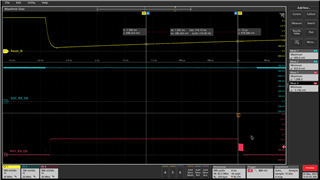

2.您还能否分享有关通过 MDIO 读取 PHY 寄存器的故障症状的更多详细信息、但以太网和 LED 的功能异常?

只有链路连接失败吗?在不同通过/失败的情况下读取寄存器转储时、寄存器配置是否有任何差异?

谢谢。

我们在此处通过 E2E 进行讨论。

Matt 的答复: