请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:TCA39416 工具/软件:

尊敬的团队:

在上述数据表中、为了获得有效的逻辑高电平、该值必须超过输入端口的 VIH。 要获得有效的逻辑低电平、请参阅

值必须小于输入端口的 VIL。

但没有具体提及 VIH 和 VIL。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的团队:

在上述数据表中、为了获得有效的逻辑高电平、该值必须超过输入端口的 VIH。 要获得有效的逻辑低电平、请参阅

值必须小于输入端口的 VIL。

但没有具体提及 VIH 和 VIL。

尊敬的 Thrinesh:

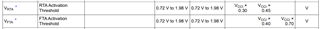

看起来我们仅为 OE 输入提供 VIL 和 VIH。

但我们还提供了 VRTA 和 VFTA 触发电压阈值。

一旦达到电压阈值、就会触发上升时间加速器(上升沿-低电平到高电平)或下降时间加速器(下降沿-高电平到低电平)。 RTA 拉至 VCC、FTA 拉至 GND。 该器件是一个 passFET。 当拉低一侧时、输出为高于输入的 Vrds_on 压降。 释放总线时、内部 PU 电阻器将对器件的每一侧进行 PU。 这会导致内部 passFET 变为高阻态、并且两侧都会看到各自的 PU 电压。

请参阅器件的内部结构:

此致、

Tyler