主题中讨论的其他器件:ADS131M04

工具/软件:

尊敬的团队:

我已通过相同的 SPI 线路 (MISO、MOSI 和 SCLK) 将 2 块 ADS131 EVM 板(使用外部电源)连接到 MCU。 两个 ADC 的 DRDY 和 CS 连接到单独的 GPIO。

OSR I 保持 512 (8kSPS)、

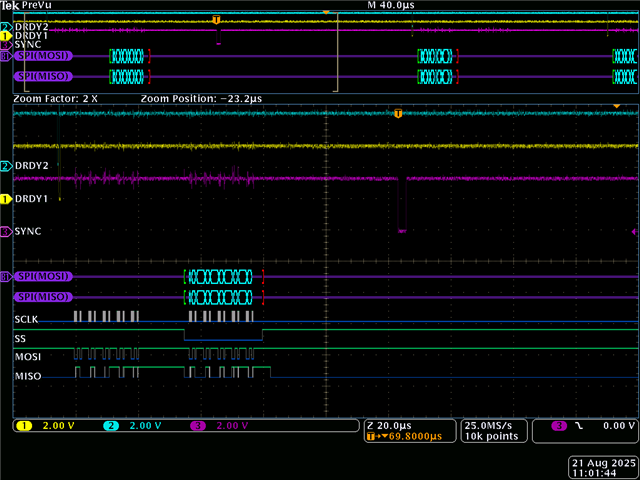

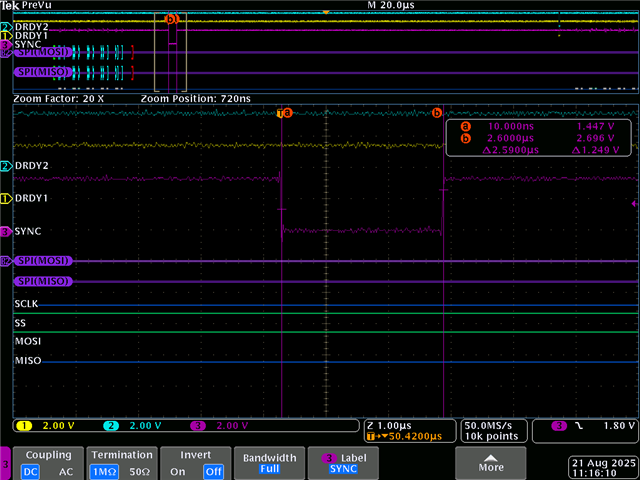

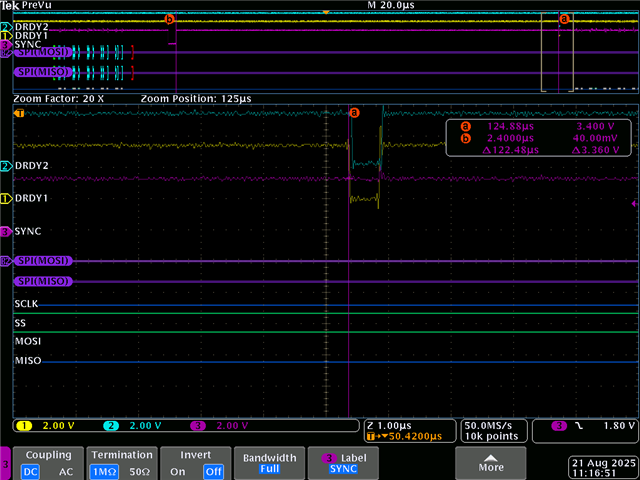

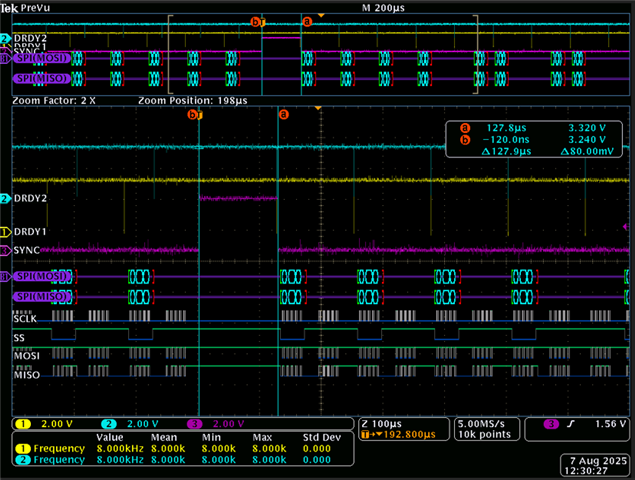

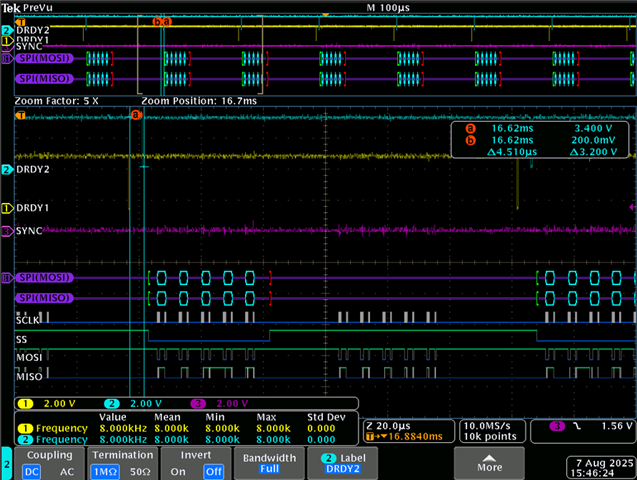

在切换 Sync 引脚之后、两个 ADC 都将保持同步、但经过一段时间后、两个 ADC 都会缓慢退出 SYNC。 我正在监控 ADC 和以下两个器件的 DRDY 信号、我附加了 SYNC 切换后和同步 1 分钟后的屏幕截图。

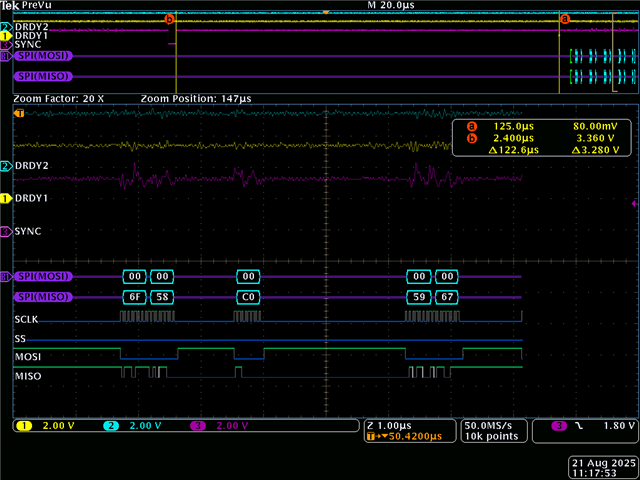

SYNC 切换后

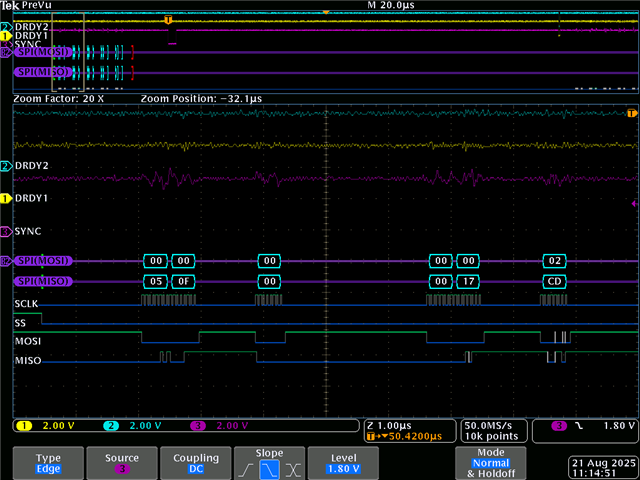

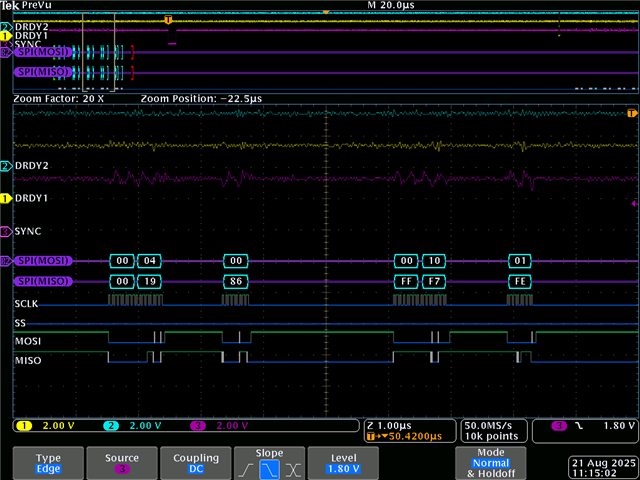

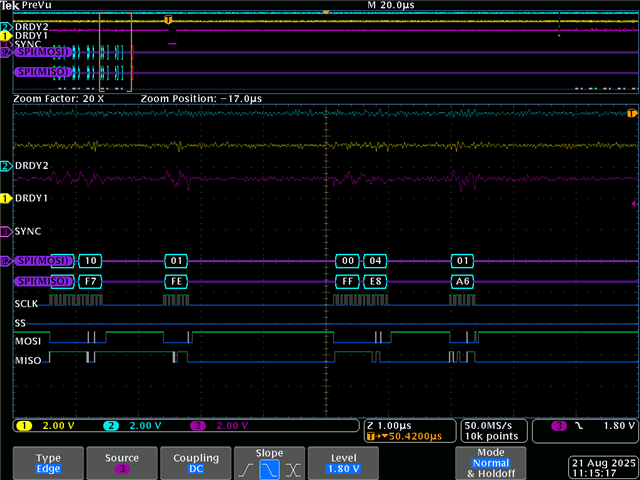

2.一分钟后,两个 DRDY 之间的切换~4.5us。

如果这种行为很常见、那么我们需要以何种速率同步器件?

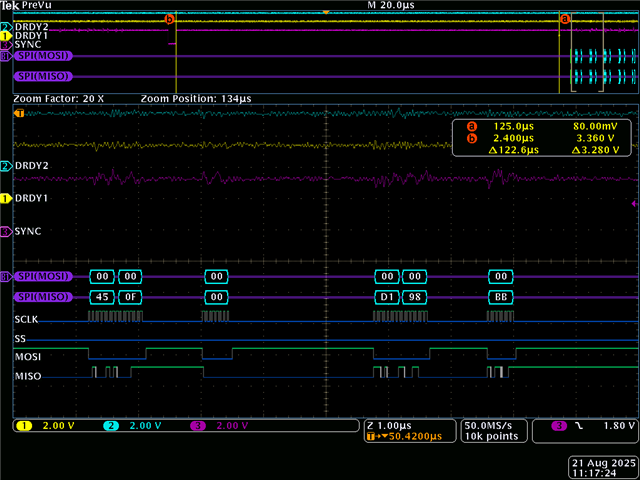

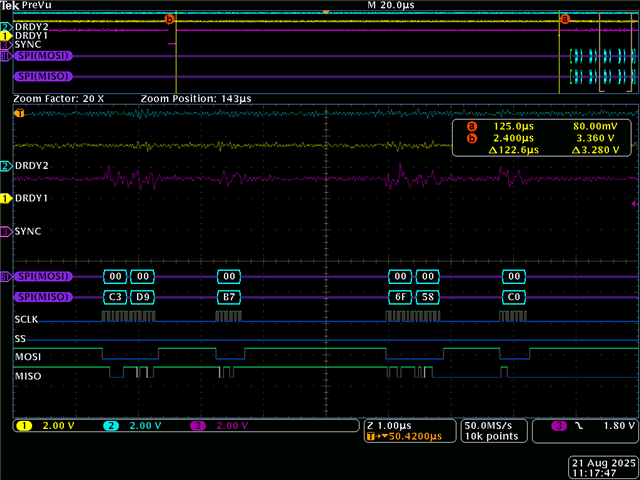

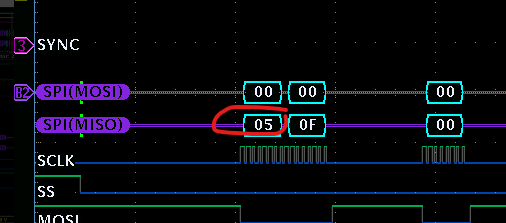

此外、我已经看到、同步完成后、在两个 ADC 上获得的下一个响应有时会发生变化。 我在发送同步信号的多次试验中检查了该结果。 即使未重新配置 ADC 或未提供复位信号、也会设置状态寄存器中的 RESET 位和 REG_MAP 位。

此致、

Shraddha