Other Parts Discussed in Thread: DS100MB203, DS280DF810, DS250DF230, DS560DF810

主题中讨论的其他器件: DS280DF810、 DS250DF230、 DS560DF810

工具/软件:

Gooday,

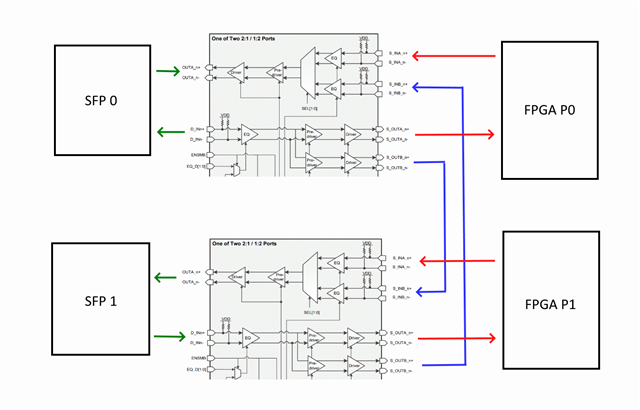

我的设计 在 FPGA 主机和 2 个 10GBASE-T1 PHY 之间使用 DS100MB203、其中 SERDES 配置为 10GBASE-R

/cfs-file/__key/communityserver-discussions-components-files/138/1108.UMAR_2D00_10G02.pdf

DS100MB203 和 PHY/SFP 端口之间有一个无源多路复用器、用于选择要使用的端点。

在 PHY 模式 (PHYTX/RX) 下、该接口以全速从 FPGA 传输到 PHY、但数据包会丢失、并且在通过 DS100MB203 从 PHY 传输到 FPGA 时会出现错误。

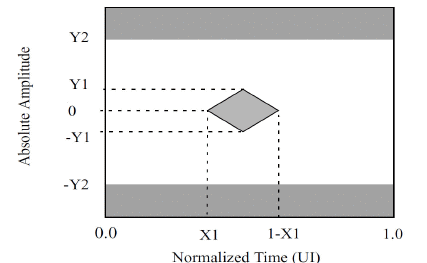

上面的是 PHY 的发送器眼图模板图片。

Y1 和 Y2 分别最小为 170mV 和最大为 425mV。

您能否建议多路复用器应具有哪些设置、或者我可能错过了设计中的任何设置?

注意:

我已在 CH4 的 MUX (D_IN0–S_OUTA0) 中添加了 I2C 寄存器、这是其中一个接收路径。 将 EQ 或 DEM 寄存器更改为高于 0 似乎会停止全部流量、VOD 和 RXDET 寄存器似乎没有影响。

此外、当我将手指放在 SERDES 布线上时、这似乎可以减少错误数量、在某些情况下可以将它们全部移除。 也许这点指的是某种东西。

如有任何帮助、将不胜感激。

谢谢你