Other Parts Discussed in Thread: PCF8574

部件号: PCF8574

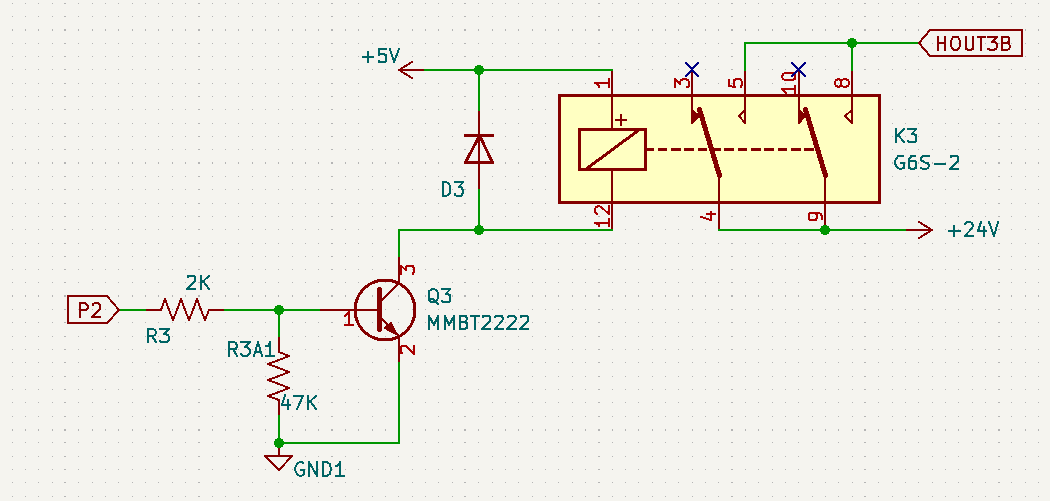

您好、我有一个定制 PCB、其排列如下

P2 是 PCF8574 引脚。

处于高电平时、R3 左侧和 GND 之间读取到大约 0.75V 的电压。 不足以激活 MMBT2222。

是否可以修复删除 R3A1 的问题?

任何建议都将得到采纳。

BR

Juan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Juan:

PCF8574 具有弱上拉 FET。 其 IOH 介于 30uA 和 310uA 之间。

电阻分压器电路看起来提供 5V /(47000 + 2000)=~102uA 的拉电流。

因此、当您决定驱动高电平时、只能读取 0.75V 的电压。 考虑使用具有更强大 PU 驱动器的 I/O 扩展器、例如 TCAL6416PWR。 其 IOH 可以驱动几 mA 的电流。

此致、

Tyler

尊敬的 Juan:

一旦 在 PCF8574 VDD 输出 1 为高电平、只要施加 3V3、就会出现有线问题、直到我通过软件将其置于低电平。

这似乎是合理的。

器件上电时应将 GPIO 用作输入。 为了将 IO 设置为输入、您可向器件写入全部 0xFF。 这是上电时的默认状态、因此一旦施加 3V3、输出 1 就会为高电平、直到您通过 I2C 写入驱动为低电平。

忘记了、R80 被删除了、因为 esp32 GPIO12 存在闪存干扰。 不需要中断引脚、因为不需要读取、只需写入高电平或低电平。 这可能是个问题吗? GPIO12-int 连接可以完成已删除

/INT 可以保持悬空、因为这是开漏输出。

如果 P2 用作输入、则不应保持悬空。

此致、

Tyler

尊敬的 Juan:

上电期间、在软件将 P1 设为低电平之前、仅 P1 为高电平。 如果和执行器由此引脚控制、这将在几秒钟内失去控制。

PCF8574 器件通过弱 PU 源上电至 VCC。 电流强度约为 100 μ A。 这相当于 10k Ω 的 PU 强度。 每个 IO 都以这种方式上电。

这个 100uA 电流源可以通过从器件外部灌入电流来克服。 这就是系统中其他地方的某些器件将 IO 驱动为低电平的方式。

我可以说这是预期的行为、您可以确定从外部在每个引脚上灌入的电流为~μ A。 如果您需要更强的 VCC 上拉高电平、请考虑添加外部上拉电阻、以使 IO 保持在更强的逻辑高电平状态。

此致、

Tyler