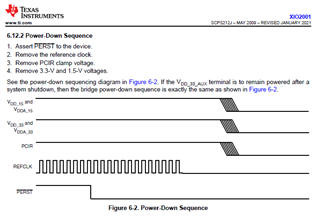

从数据表中,断电顺序定义如下。 没有根据加电顺序定义定时元件。

在卸下 PCIR 和电源滑轨之前,是否需要停止 REFCLK? 是否有一段时间时钟必须处于非活动状态,然后才能消除电压。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

从数据表中,断电顺序定义如下。 没有根据加电顺序定义定时元件。

在卸下 PCIR 和电源滑轨之前,是否需要停止 REFCLK? 是否有一段时间时钟必须处于非活动状态,然后才能消除电压。

您好纳赛尔,

非常感谢您的回应。 在我的应用程序中,VDD_33和 PCIR 由为时钟生成设备 LMK00334RTVT 供电的同一导轨提供。 LMK00334RTVT 设备的 REFOUT_EN 被向上拉至同一3V3导轨以永久启用该设备。 时钟 电源和 桥接设备 电源轨将以相同的速率衰减。 在导轨耗尽之前的某个时刻,我希望时钟停止产生。 这是否符合设备的要求,或者在 VDD_33和 PCIR 电压超出其工作范围之前是否需要移除时钟?

此致,

丹

你好,丹,

已检查 LMK 数据表,我认为您无法控制 CLKOUT_EN#或 CLKIN_SEL 以停止时钟。

在 VDD_33或 PCIR 消失之前,要拆除或停止的时钟是一种很好的设计实践,是有意义的。 但是,在您所描述的情形下,尚未对零件进行特征描述或检查。 我认为这可能会奏效,因为 LMK 短路保护将启动-即使 REFCLK 在 VDD_33之后消失。 然而,这种情况并没有得到体现。

此致,纳赛尔