https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1084435/sn65hvd24-sn65hvd24

部件号:SN65HVD24“线程:测试”中讨论的其它部件

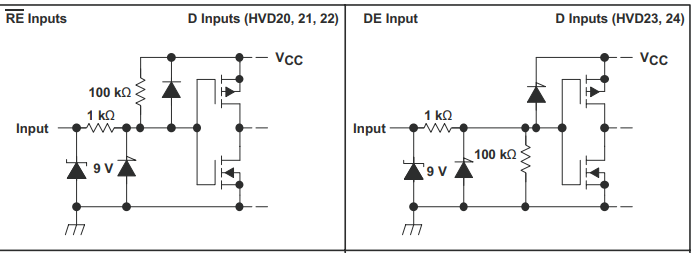

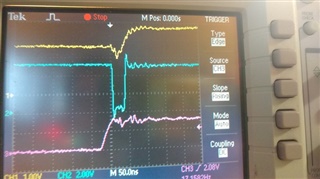

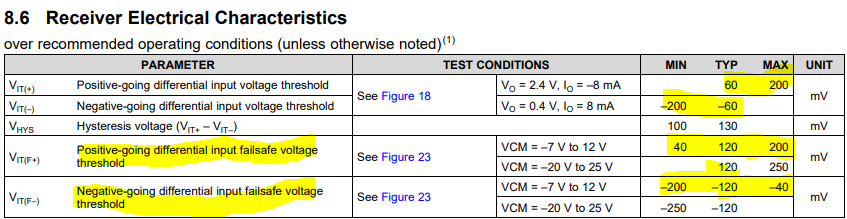

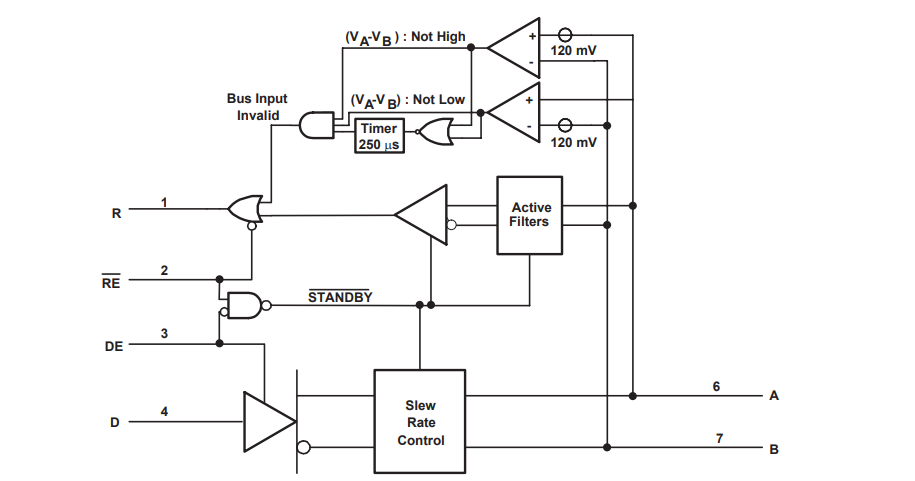

我们正在尝试在我们的应用程序中使用 SN65HVD24D (例如 Exar XR33055或 Maxim MAX33071EASA +),但由于 UART 错误而失败。 速度仅为1Mbps,总线具有外部偏置。 我怀疑原因是当传输启用设置为高(/ReceiveEnable 为低)时输出出现故障。 故障很短(仅约40 ns),但由于 UART 报告噪音错误,我认为这是一个问题。

您以前是否见过这种故障?