您好-

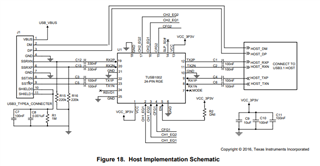

我们正在尝试为TUSB1002 芯片布局跟踪,我正在查看TI文档中的设计建议。 其中指出:

每个线对之间至少应间隔3倍的信号轨迹宽度。

但是,建议的迹线宽度为4mil,阻抗为90。

这毫无意义。 通过我们的计算和板计算器,我们无法获得这些数字,甚至90欧姆也无法接近

如果您需要一些案例的附加数据:FR-4,介电常数:4.05 ,铜厚度:384, 035 mm 介电厚度3.5mils

我们尝试了4种不同的产品,一种是主板制造商提供的,以获得他们的确切数据。 然后使用一些在线工具来查看结果,并仅为规范手动计算结果。 它们都是一样的。 下面是一个在线示例: https://www.everythingrf.com/rf-calculators/differential-microstrip-impedance-calculator

https://www.everythingrf.com/rf-calculators/differential-microstrip-impedance-calculator

https://impedance.app.protoexpress.com/

关于这种情况的另一个问题是:不同的文档规定主机应位于AB端,而有些则应位于CD端。 请您也说明一下这一点吗?