主题中讨论的其他器件:SN65DSI83

大家好、团队、

我的客户在其应用中使用 SOC->SN65DSI83->DS90UB927->DS90UB928 (显示模块)。

显示公司遇到闪烁问题、 并坚持根本原因是 H-空白在928 LVDS 输出下存在变化。

但927/928器件使用内部 PCLK 并与输出同步、因此不会有差异。

因此、我的客户询问 SN65DSI83器件是否能够生成一点 Hblanking 参数变化。

您可以帮助我回答客户的问题吗?

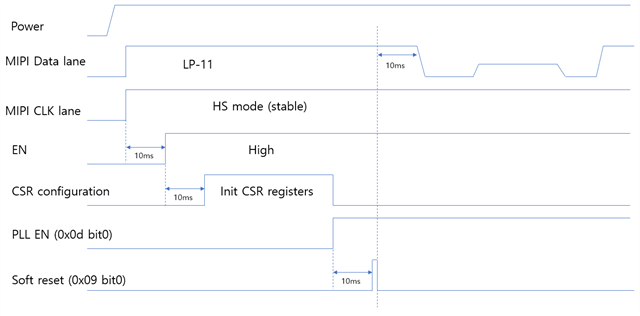

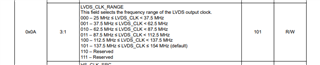

随附 DSI 调谐器设置和时序信息。

e2e.ti.com/.../9_5F00_2inch_5F00_set.pptx

谢谢你。