主题中讨论的其他器件: PCA9517、 TCA9800、 TCA9517

各位专家,您好

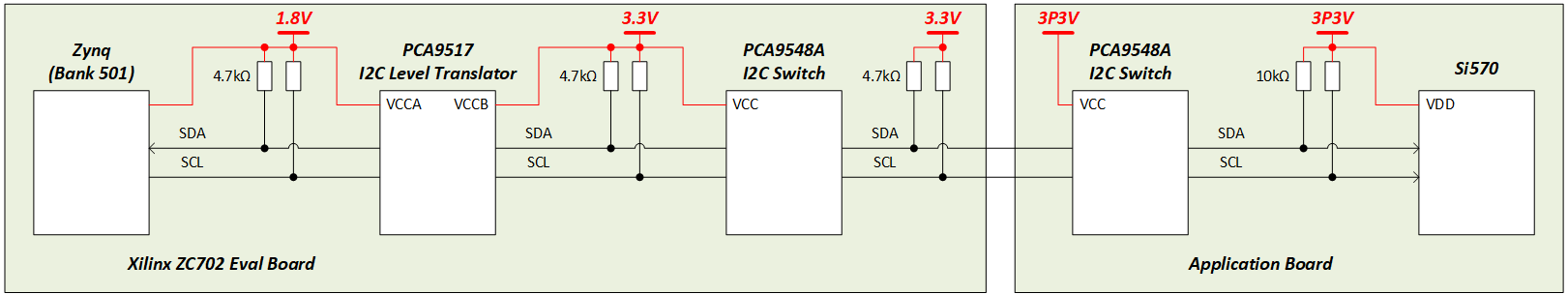

我有一个用于驱动多个 Si570A 器件的应用。 遗憾的是、Si570A 具有一个非标准 i2c 接口。 其逻辑0的阈值为0.5V 或更低、而不是 VDD 的标准30%(大约为1V 或更低)。

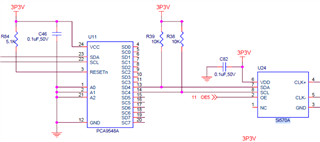

PCA9548A 输出大约0.5V 的低电压、这正是裕量。 有时、我的设计中的某些 Si570没有响应。 较弱的上拉电阻(较大的上拉电阻器和将 Vcc 从3.3V 降低到3.15V)有所帮助。

我想知道,您是否可以推荐一种将时钟输出降低到明显低于0.5V 的方法,以获得一些裕度。

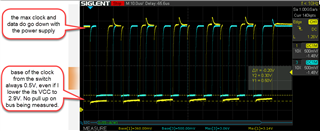

这是驱动 Si570的 PCA9548A。 时钟信号(以蓝色显示)不会低于0.5V。

请告诉我您的建议。

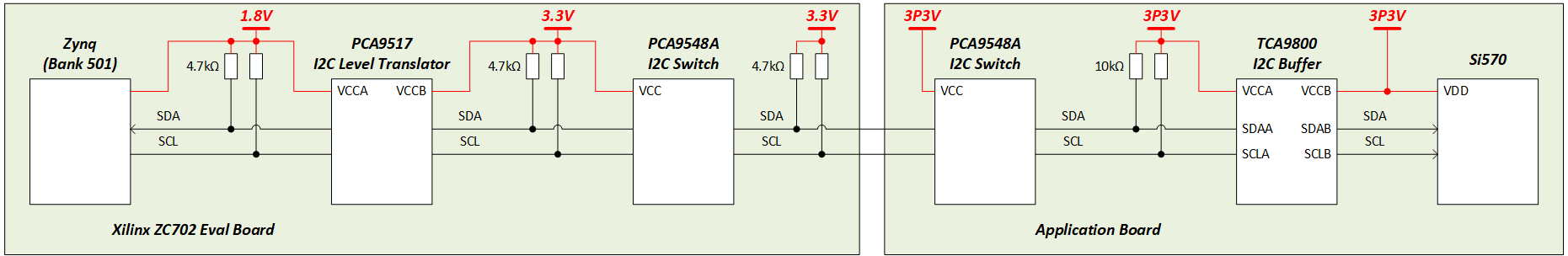

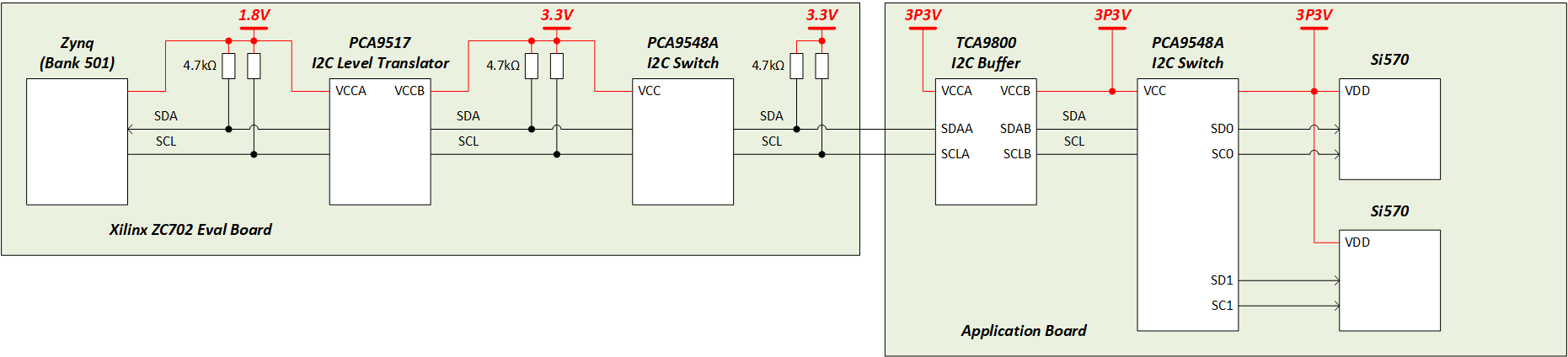

是否可以采取措施来改进这种器件组合?

是否有可提供较低逻辑0电压的替代 I2C 缓冲器?

感谢你的帮助。

此致、

Jim B